Other Parts Discussed in Thread: , DAC38RF82

I have a DAC38RF89EVM board connected to a KCU105 board via the HPC FMC connector. I am following this guide on running an example reference implementation.

I have programmed the FPGA and connected to it with HSDC Pro. I generated a waveform like in the guide and loaded it to the FPGA.

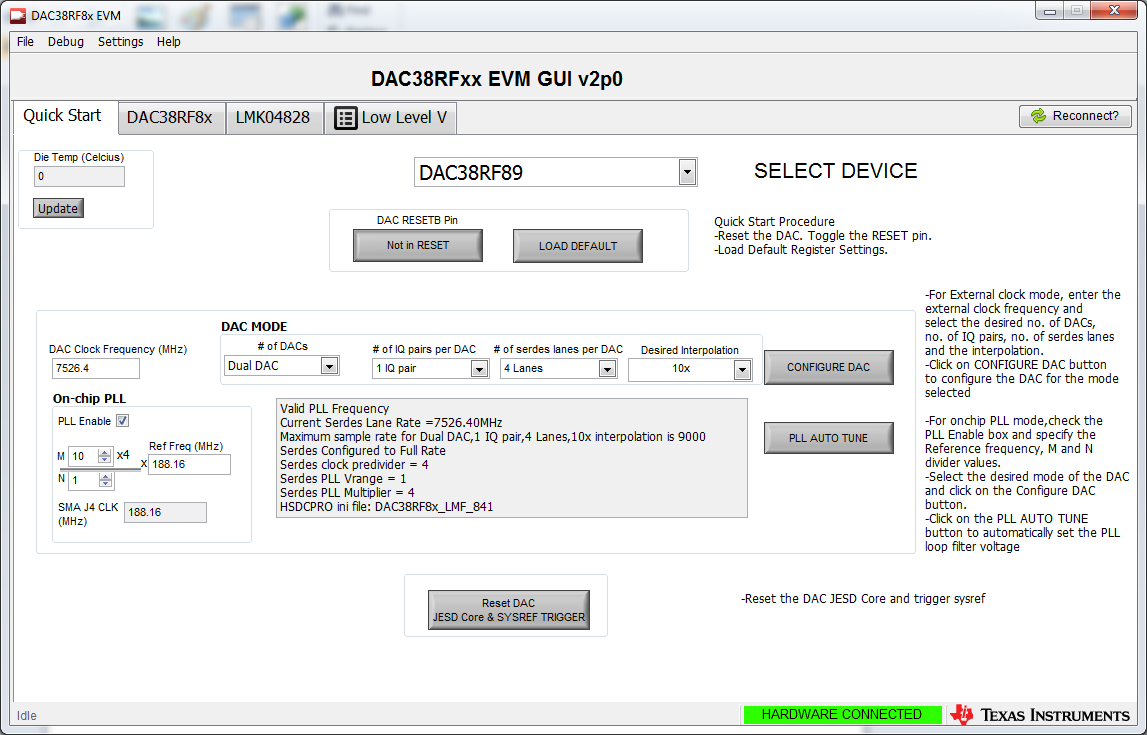

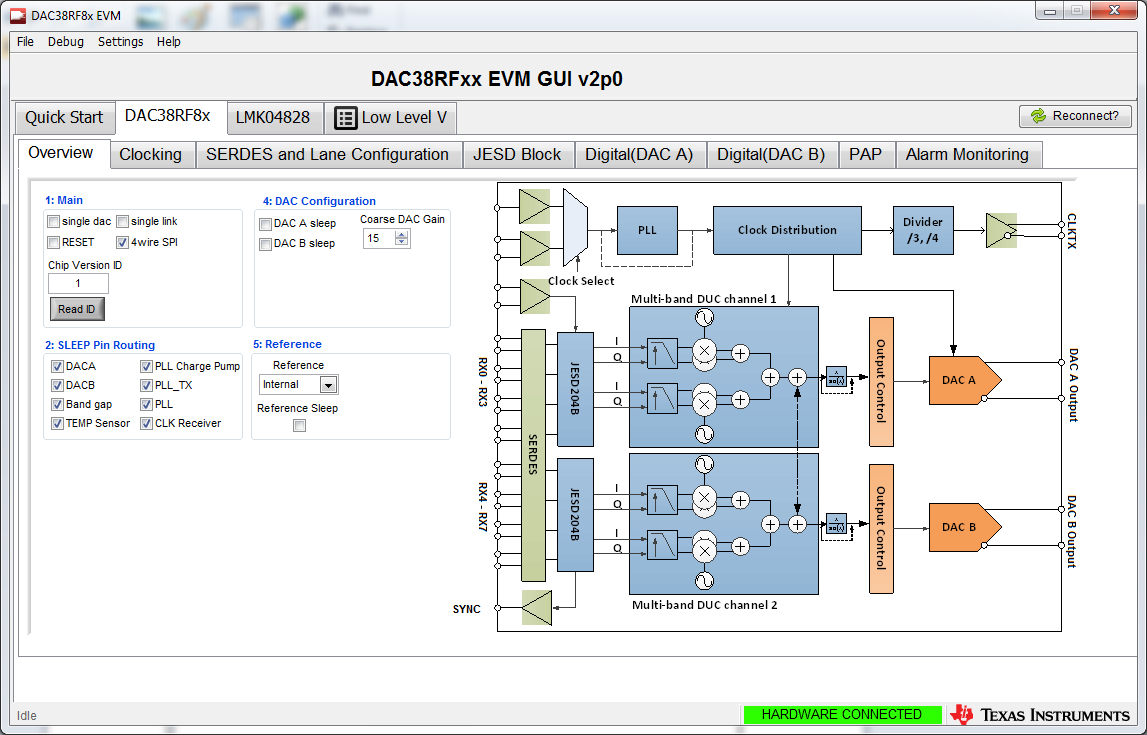

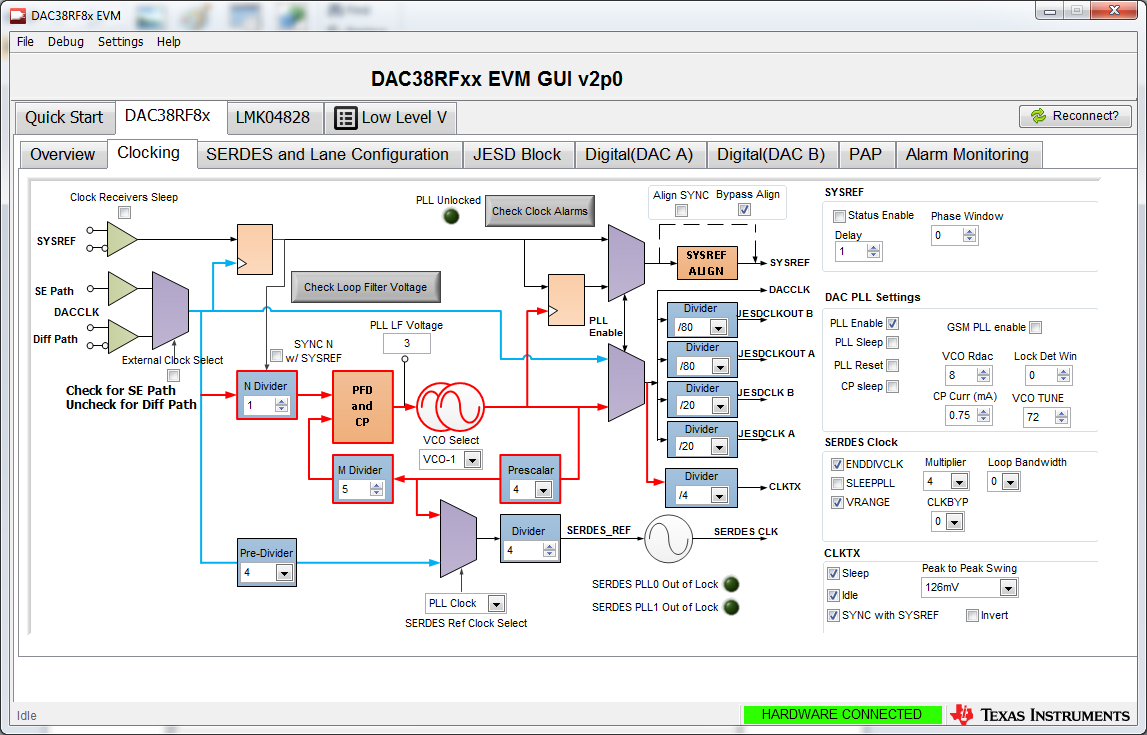

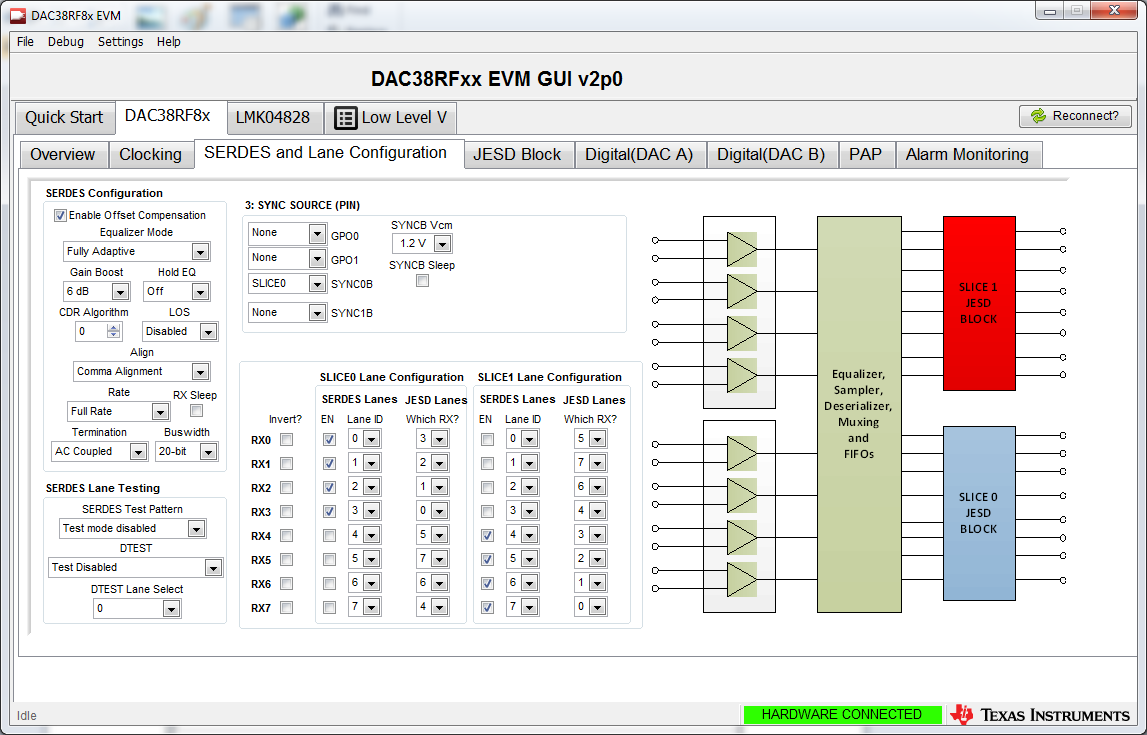

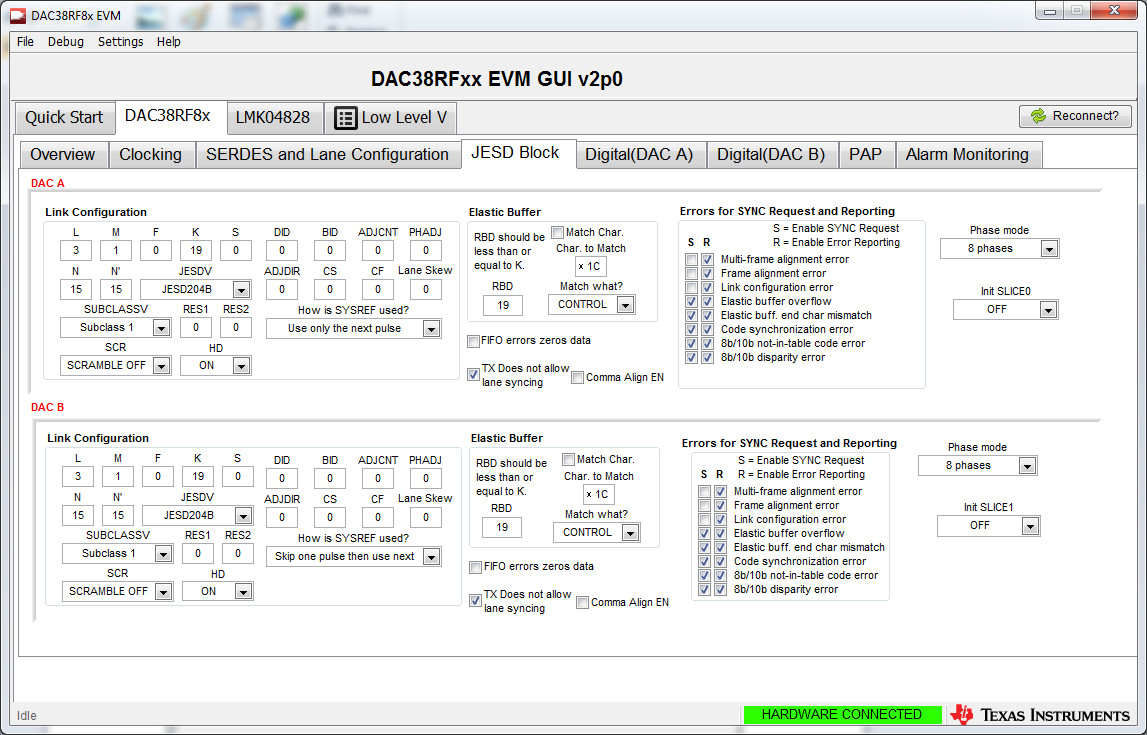

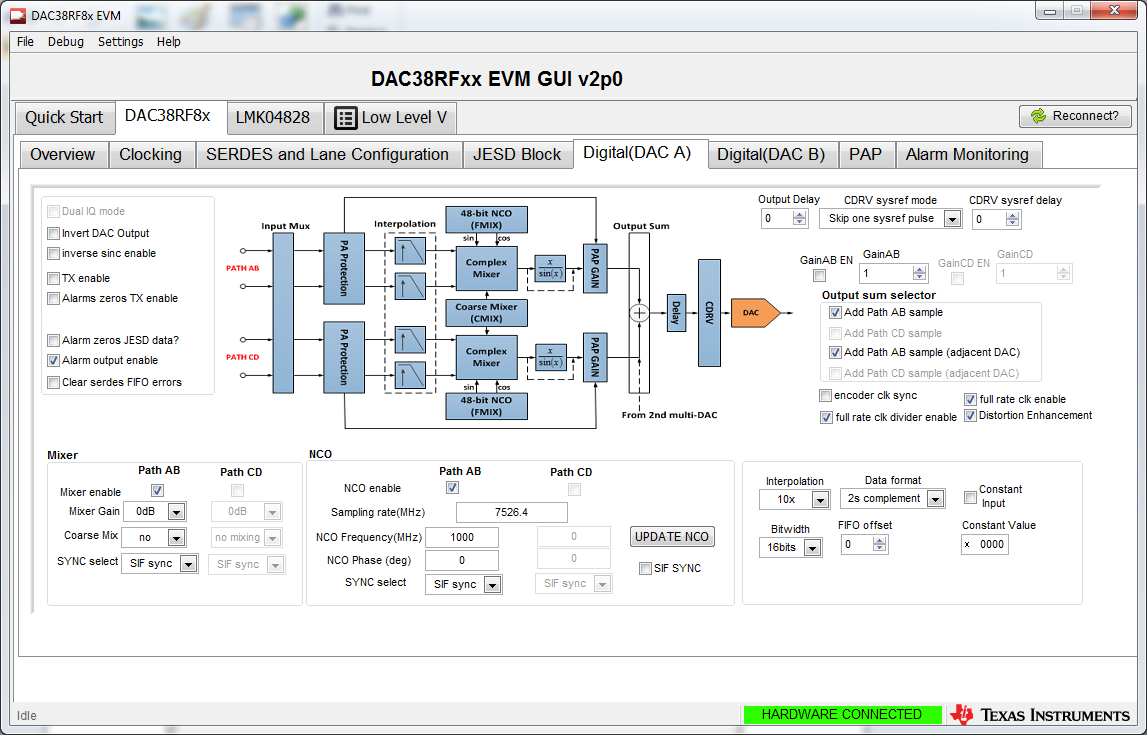

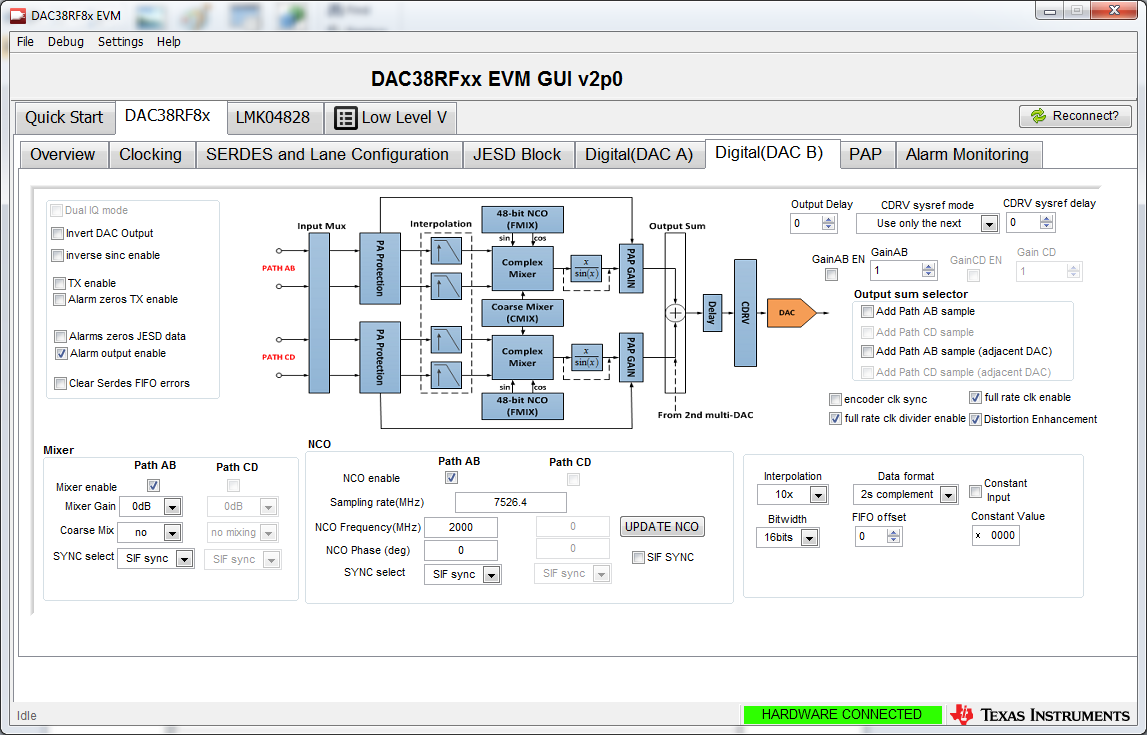

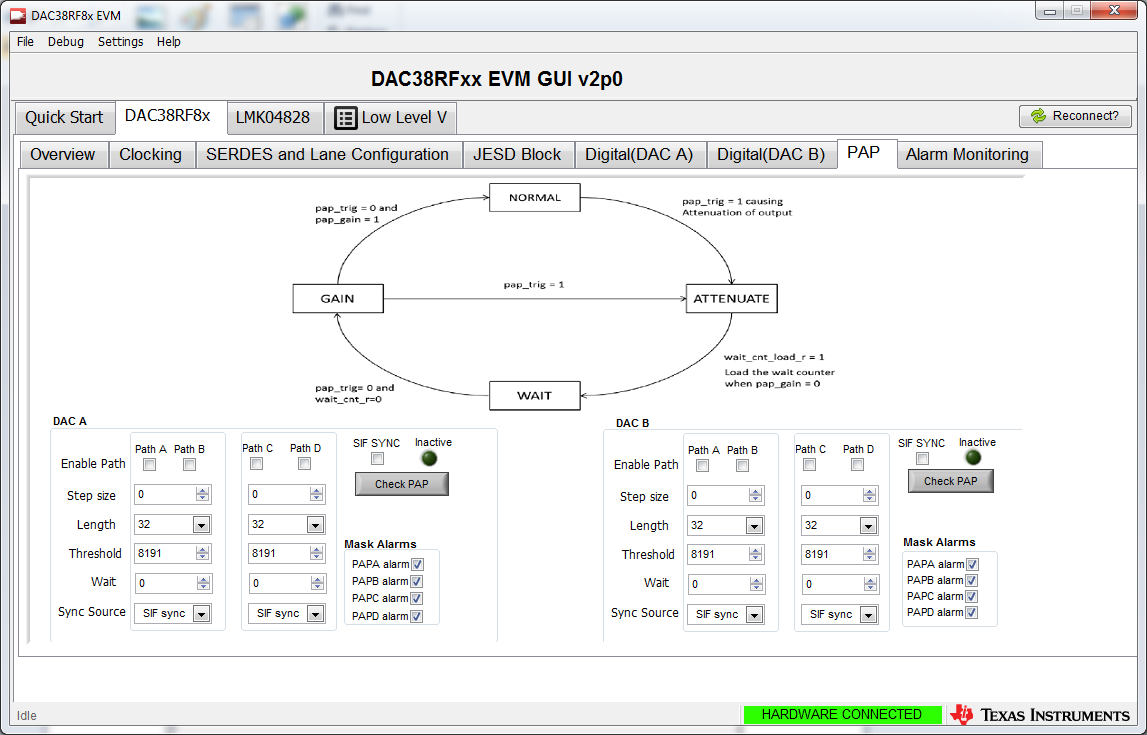

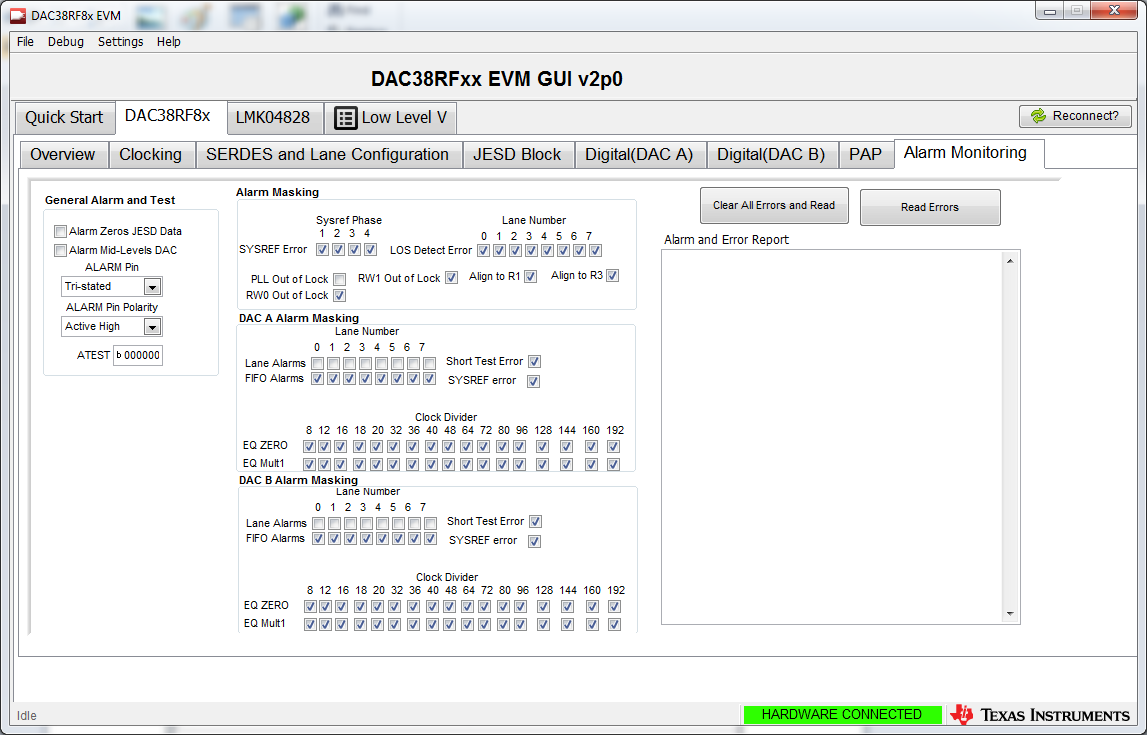

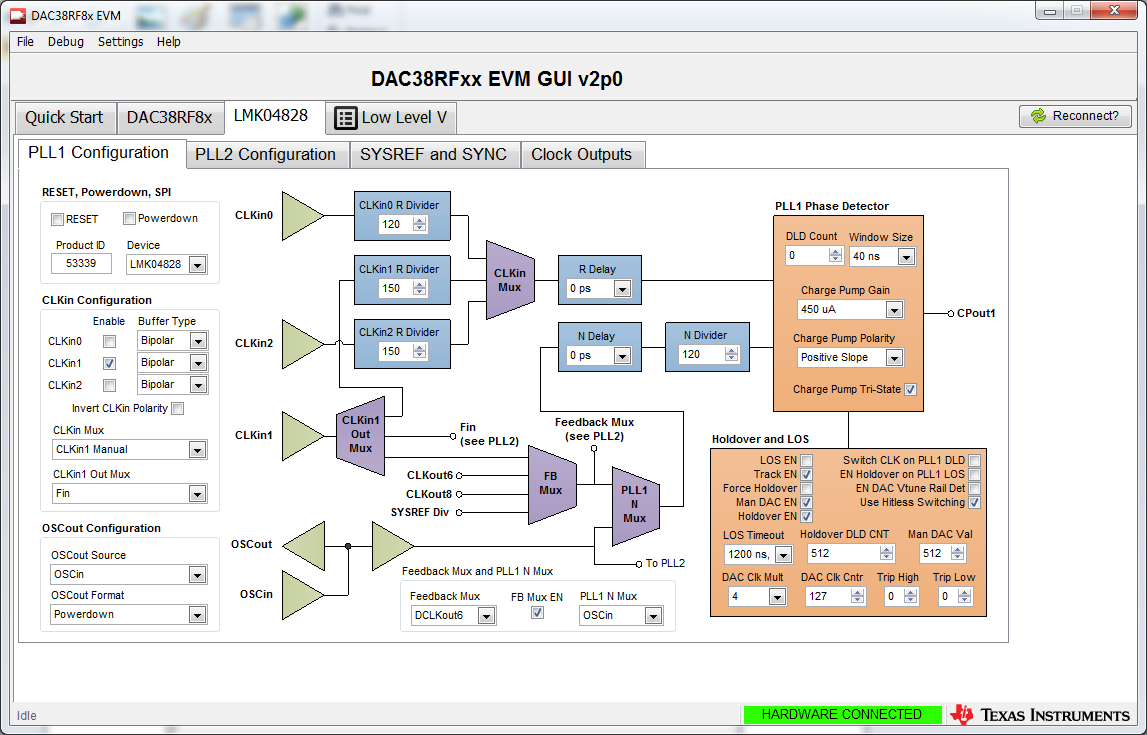

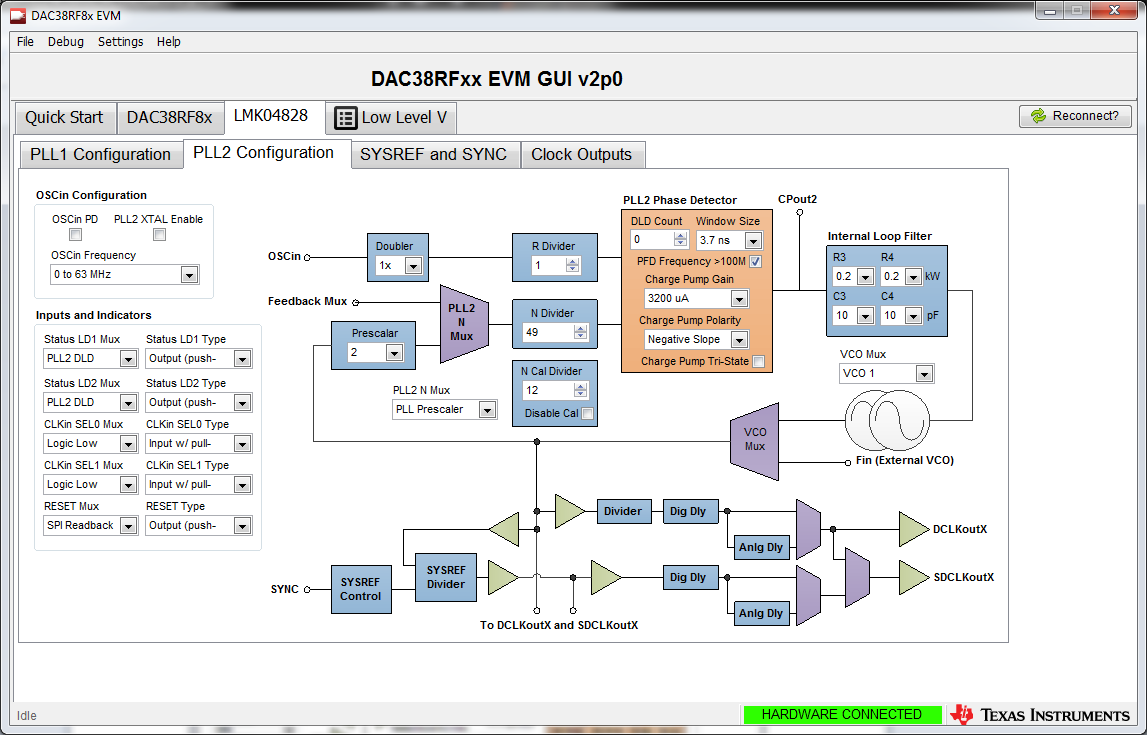

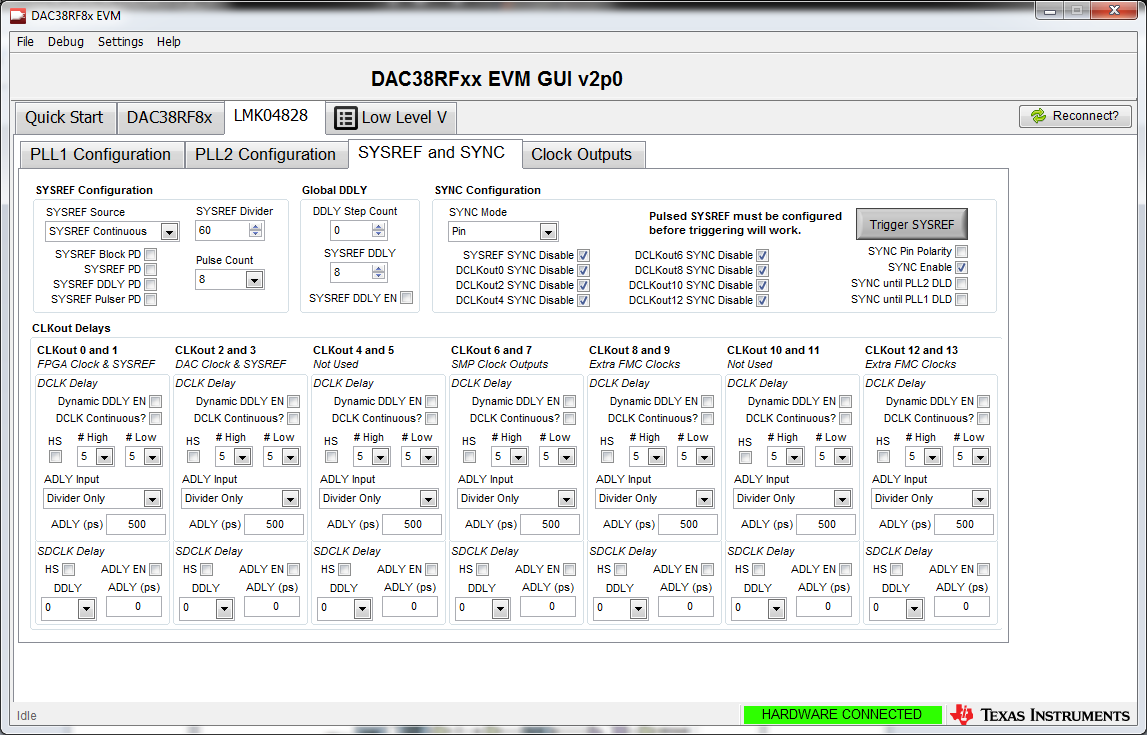

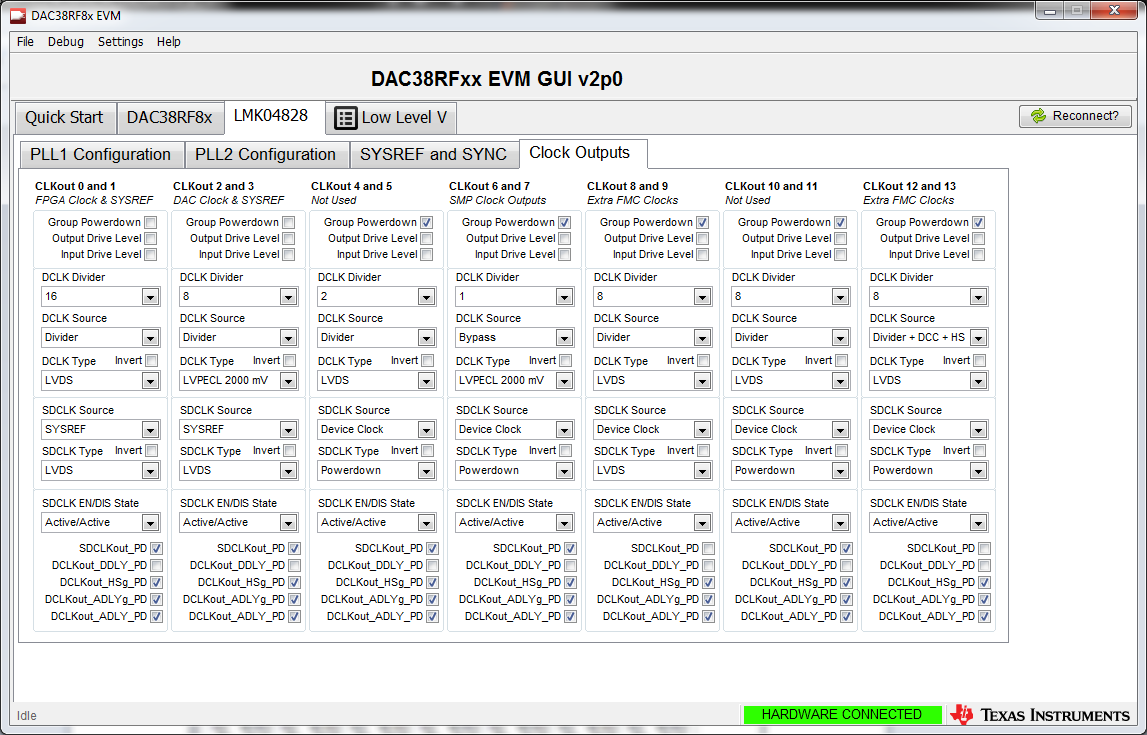

I used the DAC GUI software to connect to the DAC38RF89EVM and configured it according to the reference guidelines, except using DAC38RF89 instead of DAC38RF82.

It's the 2nd to last step (pg. 34, #14) where everything goes wrong. When I hit "Reset DAC JESD Core & SYSREF TRIGGER", the JESD core on the FPGA seems to freeze and isn't responsive. No waveform appears.

I used a debugger to check out the JESD IP core register interface, and all of its settings (lanes, bytes per frame, # frames, etc.) match correctly with what is in the DAC GUI. After the sync event, all of these registers become stuck in reset.

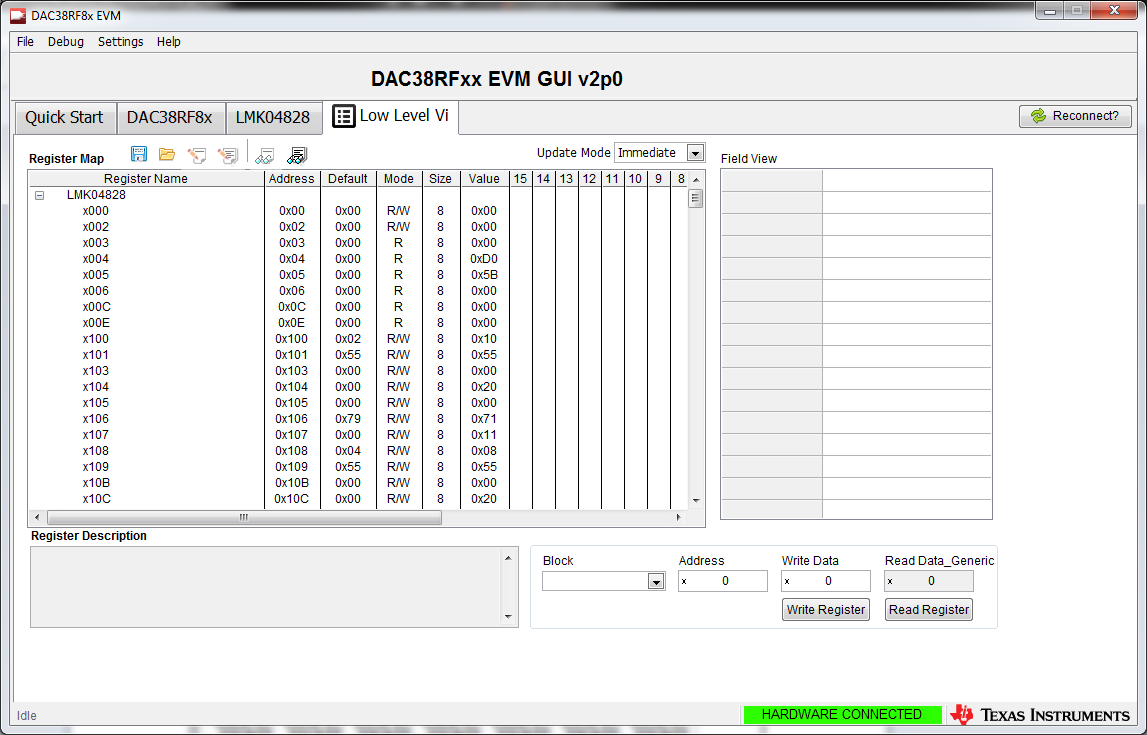

I stepped through the DAC/LMK register writes that occur after pressing "Reset DAC JESD Core & SYSREF TRIGGER" and found out that the sync occurs when the LMK register 0x143 gets written to. Specifically, it gets written with a value of 0x31 and, from the datasheet, it is inverting the JESD sync signal. It is at this moment that the JESD core freezes.

Anyone experience a problem like this? Any potential causes for the issue? Could this be an issue with Xilinx JESD core?