Other Parts Discussed in Thread: DLP2021-Q1, , DLPC230-Q1

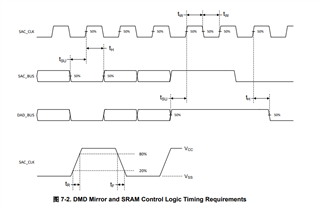

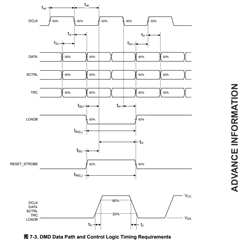

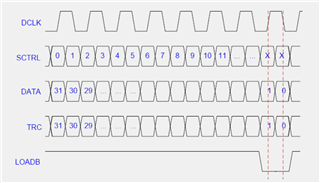

Because I want to choose my own controller to control DMD, I want to know more about the control timing of DMD.Based on the following DMD timing diagram provided by the DLP2021-Q1 document, I can't seem to figure out how to control the DMD display. I would like to know if there is a more detailed timing or content of DLP2021-Q1 control? Thank you so much for your help.