Other Parts Discussed in Thread: DLPC3478, DLPC3438, DLPC3470

Hi,

We have been testing the custom DLP controller board which is using DLPA2005.

During the EMI radiation pre-test in an EMI chamber, we've found that there is a problematic observed frequency at around 330 MHz which is beyond the suggested limit.

As this only happens when the projector was on, we could conclude this is related to the projector related ICs, patterns, etc: e.g. DLPC3478, DLPA2005

Although we were able to easily solve the problem by properly shielding the case, we are now optimizing the circuit design to make the EMI characteristics better.

While checking the ICs' manual, we've found some interesting parts:

The DLPA2005 datasheet link is as follows:

https://www.ti.com/lit/ds/symlink/dlpa2005.pdf?ts=1692140216596

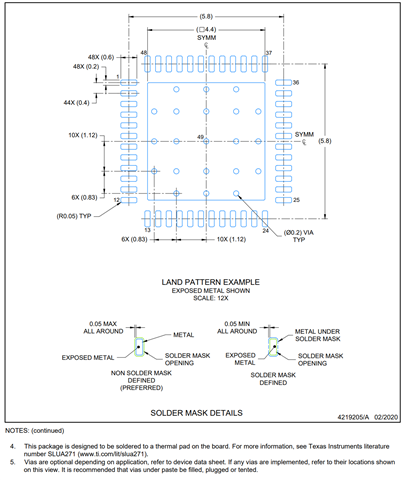

1. Via patterns (P54)

"Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented."

Can I ask the reason of providing a specific grid pattern for these VIAs? I think there must be reasons, but they are not clearly stated in the datasheet.

Note that the evaluation board is also well following this guideline.

What would happen if we don't follow the guideline?

2. Layout Guidelines (P44)

There are some guidelines on P44 and on the page, it especially emphasizes the importance of the guideline saying there would be issues in EMI if the practice is not done properly.

We wanted to narrow down the parts and during the near field probe testing, what we've found is that the radiation is more on the dmd FPCB, led cable and DLPC3478 part not from the area nearby DLPA2005.

Is this normal?

3. EMI general guidelines which is related to the custom design board which uses DLPC3478 and DLPA2005

Are there any additional materials which are related to the EMI proof design about particular parts?

(DLPC347x, DLPA2005, etc)

Thanks.