Other Parts Discussed in Thread: DLPA2005, DLPA3000

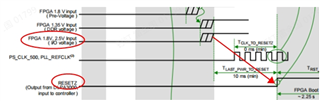

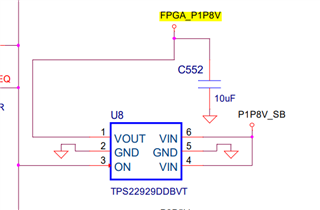

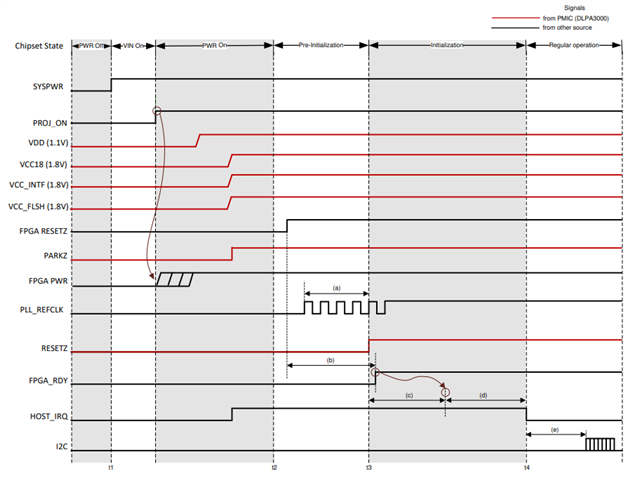

My customer is developing DLPC3436 with DLPA2005, and the power-up timing requires that resetz should be pulled up after FPGA_1.8V for at least 10ms. The power-up timing on datasheet if from DLPA3000, and I tested our DVH board which meet the timing requirements with DLPA3000. However, at our EVM board with DLPA2005, the delay is only around 2ms. This is noticed by my customer, and we found that the TPS22929 brings around 6ms delay(The same design on our EVMs). Even though we remove the TPS22929, the delay is only around 7ms. Is this timing requirements should be strictly followed?