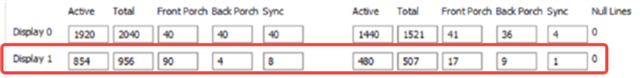

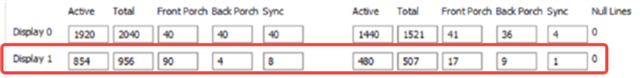

Hello, we use DLPC120+DLP3030 for display ,the output resolution is 854*480, the display timing in the following picture (different from the datasheet), I want to confirm whether this set of parameters can work normally, thank you.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello, we use DLPC120+DLP3030 for display ,the output resolution is 854*480, the display timing in the following picture (different from the datasheet), I want to confirm whether this set of parameters can work normally, thank you.

Hello Bruce,

Welcome back to the E2E forum and we hope to assist you with your questions.

We have not tested out settings outside of the datasheet so we do not know if the settings you suggested work or not and recommend you use the settings from the datasheet as these have been validated.

Regards,

Alex Chan

Thanks for your reply Alex,

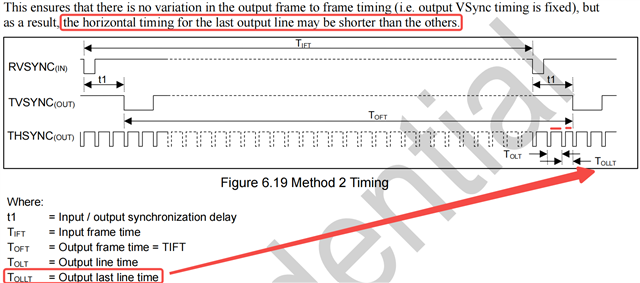

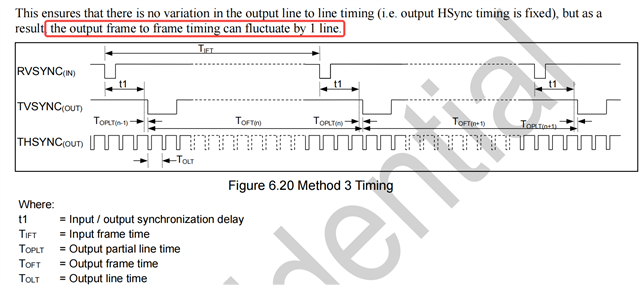

There is another problem. Our customer can only provide this set of timing parameters as input, so we need to add a video processing IC to adjust the timing to meet the requirements in the datasheet. The IC we selected has two ways for timing Synchronization, But both 2 ways have some requires of the display device. Please help to confirm whether DLPC120 and DLP3030 can meet this requirement:

1、Panel can handle a truncated line for the final line of the vertical front porch

2、Panel cannot handle a truncated line for the final line of the vertical front porch,but Panel can handle a 1 line variation in the length of the vertical front porch from frame to frame

Hello Bruce,

Is this a Texas Instruments video processing IC chip?

Unfortunately we do not have much information for a use case like this and I am not sure if the DLPC120 was designed to handle a situation like this. This may have to be something the customer will have to try out on their own as we have no way of testing this kind of scenario. Irregular Hsyncs out of specification may result in video artifacts.

Regards,

Alex Chan