Tool/software:

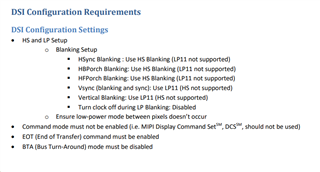

I wanted to clarify the meaning of this line in section 7.3.1.4 of DLPS035E:

"LP mode is required during vertical blanking and vertical sync."

Does this mean that the vertical and horizontal sync packets themselves need to be sent in LP mode during inactive lines, or is it sufficient to just be in LP11 during the bus idle time (and transition to HS at the start of each line for the appropriate vsync/hsync packet)?