Other Parts Discussed in Thread: DLP4710LC, , DLPA3005, DLP4710EVM-LC

Tool/software:

Hello!

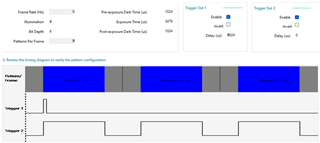

I'm using External Pattern Mode, 8-bit monochrome patterns。

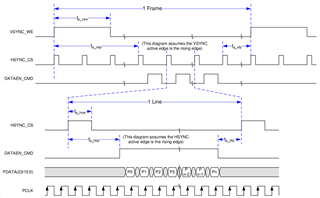

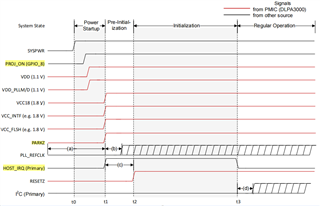

I'm uses the PARALLEL RGB interface, the timing is RGB888, and the external input is 1280*800@60hz,PDM_CVS_TE with default of active low.

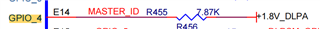

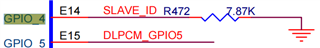

But nothing shows.The hardware architecture is dlpc3479 + dlpa3005 + dlp4710lc.

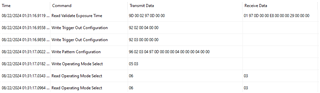

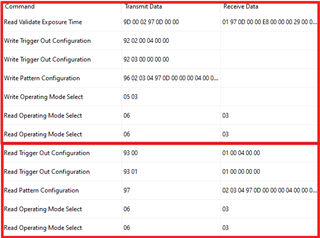

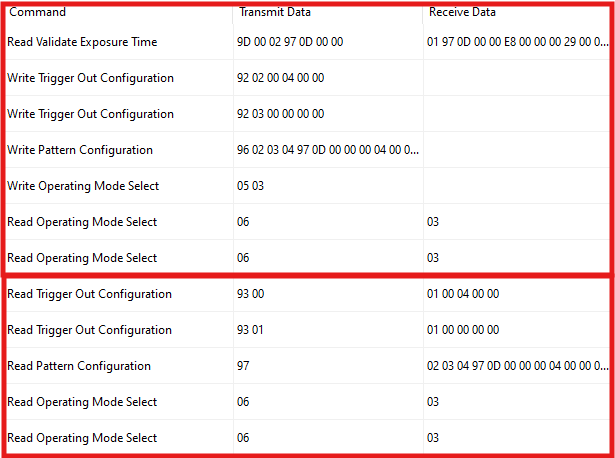

The following is the register I configured, and the corresponding value, to help me see if there is a problem。

ADDR value

8'h92 8'h02,8'h00,8'h04,8'h00,8'h00

8'h92 8'h03,8'h00,8'h00,8'h00,8'h00

8'h96 8'h02,8'h03,8'h04,8'h1A,8'h39,8'h00,8'h00,8'h00,8'h04,8'h00,8'h00,8'h00,8'h04,8'h00,8'h00

8'h05 8'h03