Part Number: SN65DP159

Other Parts Discussed in Thread: TMDS181, TPD12S016, TMDS171

Hello,

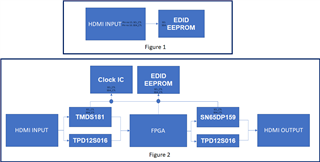

We are planning to use SN65DP159 IC to convert the TMDSTm to HDMITm and then we have connected those signals with FPGA.

For the I2C & HPD, we have used the TPD12S016RKTR level shifter.

So Can we leave HPD & I2C pins (Pin no. #4,46,47,33,39,38) of SN65DP159 IC as floating ? If no then where to connect?

We have attached the image for reference.

Thanks,

Yamini