Hello,

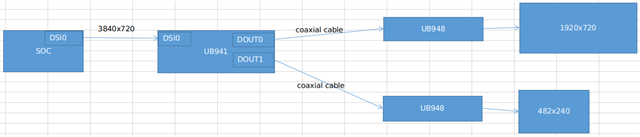

The application diagram is as following:

Superframe( before split)is 3840x720,and the customer referred to the datasheet “8.4.6.4.2.1 Asymmetric Splitting With Cropping" to split and crop the right side of superframe.

He configured the register according to " RevB_941AS_SuperFrame_Calc.xlsm (snlc064.zip)". But the results are that the panel of 1920X720 could display normally, but 482x240 can't.

Then he tried to change the superframe is 3840x320 and configured the related registers about splitting and cropping again, the 482x240 could display normally, while 1920x720 can't due to height problem.

He also tried to modify the below registers, but 482x240 also can't display.

SPLIT_CLK_SEL, SPLIT_CLK_DIV_M, SPLIT_CLK_DIV_N

DSI_HSW_CFG_HI, DSI_HSW_CFG_LO, DSI_VSW_CFG_HI, DSI_VSW_CFG_LO

DSI_PCLK_DIV_M, DSI_PCLK_DIV_N

His configuration is as following when he debugged:

uVisWidth = '3840'

uHsyncFrontPorch = '128'

uHsyncWidth = '128'

uHsyncBackPorch = '128'

uVisHeight = '720'

uVsyncFrontPorch = '3'

uVsyncWidth = '3'

uVsyncBackPorch = '3'

uPixelFreqInHz = '184757760'

bDEPolarity = '0'

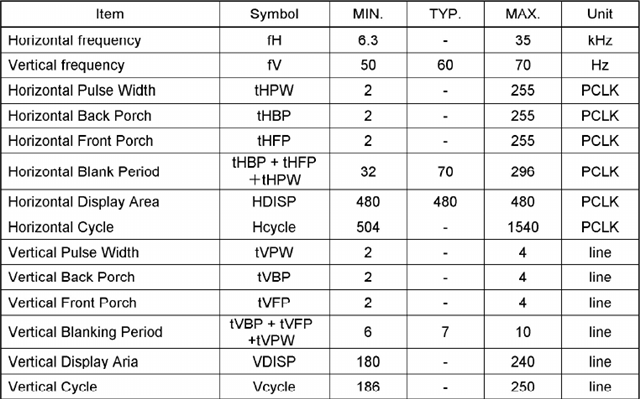

The spec of the 482x240 panel:

The configuration of DS90UB941 is:

0x01=0x08 # Disable DSI */

0x1e=0x01 # Select FPD-Link III Port 0*/

0x06=0x01 # Change deser i2c addr */

0x07=0x58

0x08=0x5A

0x03=0x9a # Enable I2C_PASSTHROUGH */

0xc6=0x21 # Step 1 of "8.3.8.1 Interrupt Pin (INTB)" from datasheet */

0x40=0x04 # Select DSI Port 0 digital registers */

0x41=0x21 # Select DSI_CONFIG_1 register */

0x42=0x60 # Set DSI_VS_POLARITY=DSI_HS_POLARITY=1 */

0x1E=0x01 # Select Port0 # set split mode, left/right 3D image, non-continuous clock mode

0x5B=0x87 # Force Splitter Mode

0x56=0x80 # Enable conversion of L/R image into alternating pixel image

0x4F=0x84 # Set 2 lane DSI

0x1E=0x02 # Select Port1

0x5B=0x87 # Force Splitter Mode

0x56=0x80 # Enable conversion of L/R image into alternating pixel image

0x4F=0x84 # Set 2 lane DSI

0x06=0x01 # Change deser i2c addr */

0x07=0x58

0x08=0x5E

0x03=0x9a # Enable I2C_PASSTHROUGH */

0xc6=0x21 # Step 1 of "8.3.8.1 Interrupt Pin (INTB)" from datasheet */

0x40=0x08 # Select DSI Port 1 digital registers */

0x41=0x21 # Select DSI_CONFIG_1 register */

0x42=0x60 # Set DSI_VS_POLARITY=DSI_HS_POLARITY=1 */

0x1E=0x01 # Select Port0

0x32=0x80 # Set IMG_LINE_SIZE

0x33=0x07 # Set IMG_LINE_SIZE

0x36=0x00 # Set crop start X position (LSB)

0x37=0x80 # Set crop start X position (MSB)

0x38=0x7F # Set crop stop X position (LSB)

0x39=0x07 # Set crop stop X position (MSB)

0x3A=0x00 # Set crop start Y position (LSB)

0x3B=0x00 # Set crop start Y position (MSB)

0x3C=0xCF # Set crop stop Y position (MSB)

0x3D=0x02 # Set crop start Y position (LSB)

0x1E=0x02 # Select Port1

0x36=0x00 # Set crop start X position (LSB)

0x37=0x80 # Set crop start X position (MSB)

0x38=0xE1 # Set crop stop X position (LSB)

0x39=0x01 # Set crop stop X position (MSB)

0x3A=0x00 # Set crop start Y position (LSB)

0x3B=0x00 # Set crop start Y position (MSB)

0x3C=0xEF # Set crop stop Y position (MSB)

0x3D=0x00 # Set crop start Y position (LSB)

0x1E=0x01 # Select Port0

0x40=0x04 # Select DSI digital page

0x41=0x05 # To reg 0x05 (TSKIP CNT)

0x42=0x36 # Set value for DSI+CLK

0x40=0x08 # Select DSI digital page

0x41=0x05 # To reg 0x05 (TSKIP CNT)

0x42=0x36 # Set value for DSI+CLK

0x01=0x00 # Enable DSI */

So the question is how to display the two panel normally? Does DS90UB941 support to modify the display timing/blanking?

Best regards

Kailyn