Part Number: DS110DF410

Dear Expert

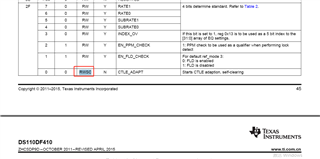

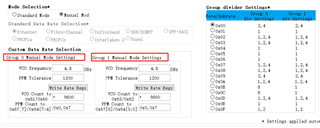

1. What is the meaning of RWSC as shown in the figure below?Is setting this bit, 0x2F[0] to 1, going into CTLE's adaptive mode?In this mode, instead of setting the EQ seting value, the device will automatically find the most appropriate value?

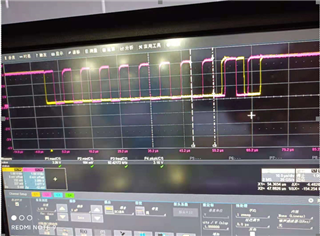

2. As shown in the figure below, when I select Adaptive Mode 1, does the CTLE Setting have to be set manually?If so, how?

3. As shown in the figure below, what are the differences and meanings between Group 0 and Group 1?The specifications don't seem to describe it.

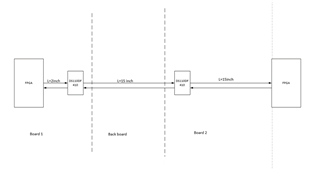

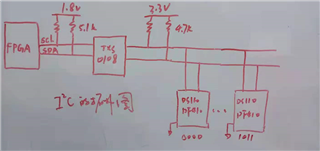

4. The following diagram is the topology of the link using DS110DF410 on our product.As you can see, we've added DS110DF410 at both the transmitter and the receiver.The routing length of each link segment is shown in the figure.Currently we are commissioning at a rate of 4.8Gbps (it is possible to increase to 9.6Gbps later)

It is hoped that the engineer of the original factory can configure a set of register tables according to the rate of 4.8Gbps and the actual wire length below (PCB plate is TU768+TU872).The Adaptive Mode 1 is sufficient.