Part Number: SN65DPHY440SS

Other Parts Discussed in Thread: DPHY440SSRHREVM

Hello,

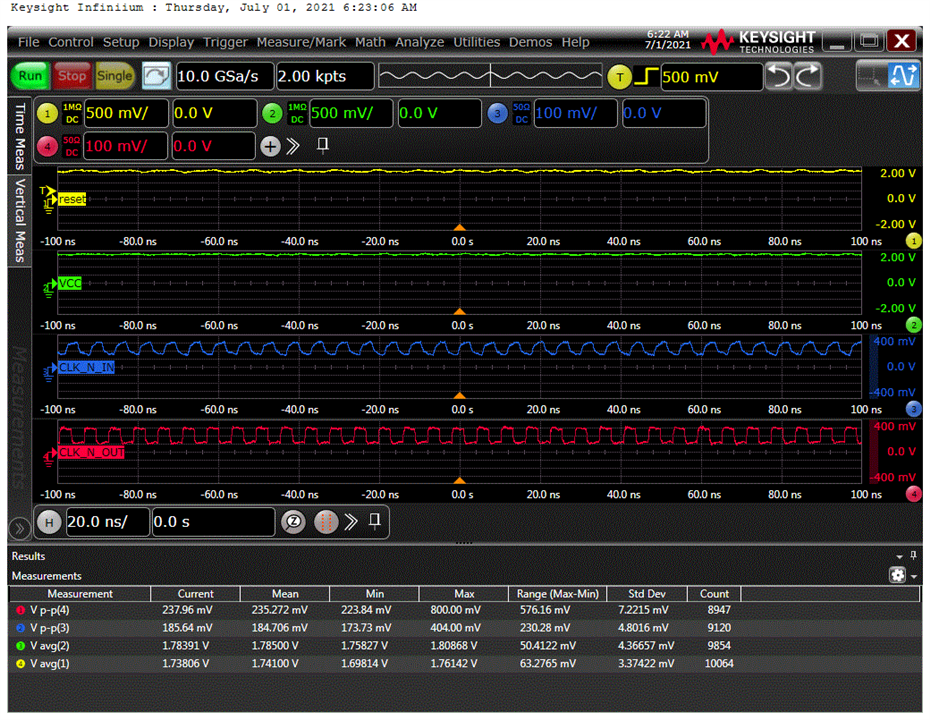

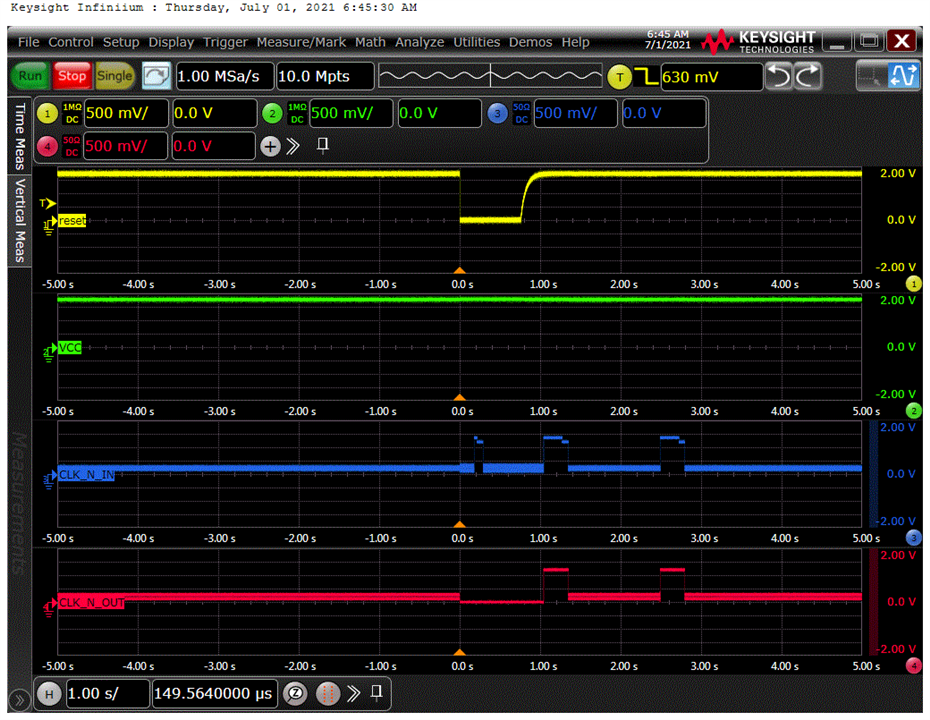

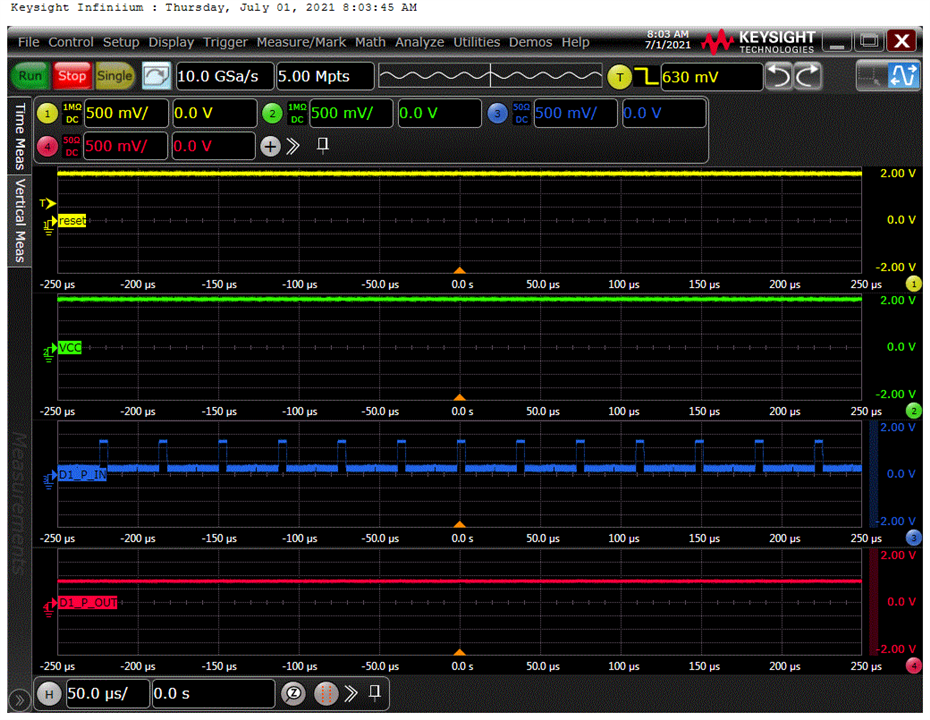

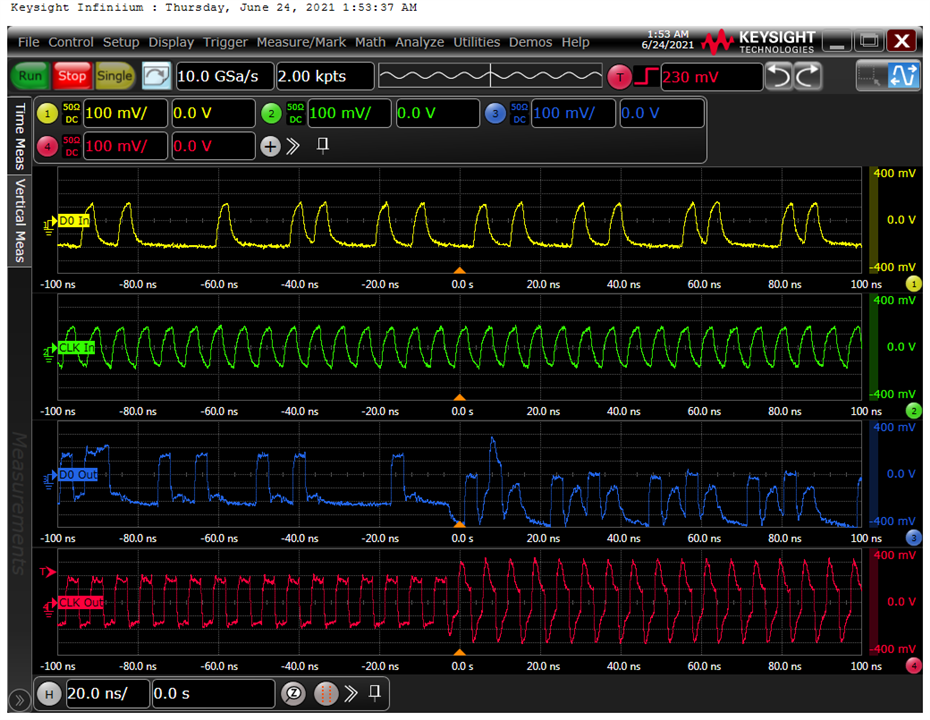

I'm running into a problem with this part. First, a little back story. I've already verified the part works in my system using the eval board. Now I've brought the Re-Timer IC onto my own PCB with the same configuration and it doesn't work anymore. I've verified Data and Clock are passing through the Re-Timer and appear to be output as expect. However, one interesting thing I've noticed is that the output driver appears to unexpectedly (and periodically) change its driving condition. Please see attached scope capture. As you can see the input data and clock signals do not change yet the output goes through a drive change.

As you can see the input data and clock signals do not change yet the output goes through a drive change.

Any help is appreciated.

Thank you,

Nathan