Hi, expert

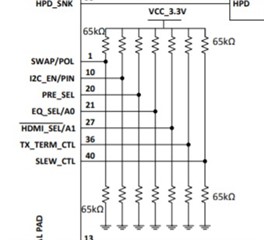

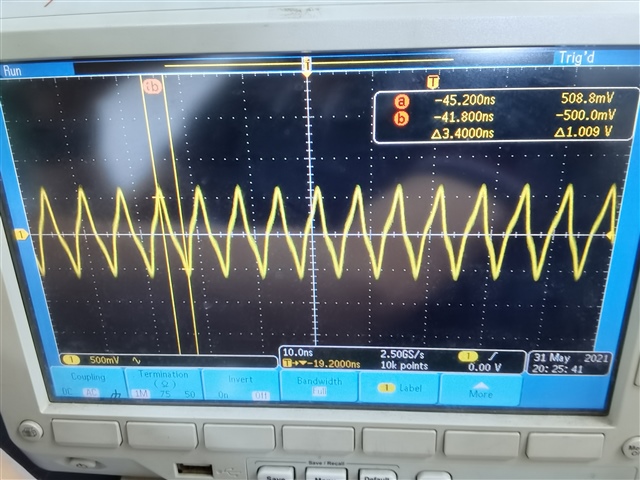

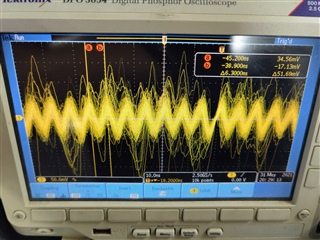

My customer met an issue on SN65DP159 --- the clock outputs are abnormal, please see attached waveforms and their schematic.

This issue happened with HDMI2.0 and HDMI1.4, and HPD_SNK is high when the issue happened.

Could you please help review the schematic and find out if there are any design errors especially the pull up and pull down pins?

And could you please tell customer which pairs of I2C should be used to debug? Thanks.

Best Regards.

Chen