Hello,

I want share my experience with DP83869HM.

I have 2 custom boards. One working Ok, other sgmii connection very unstable.

Linux ethtool -S eth0 show fcs errors.

After investigation, I found cause of not stable sgmii connection via sgmii.

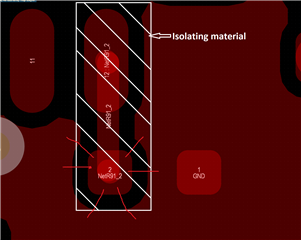

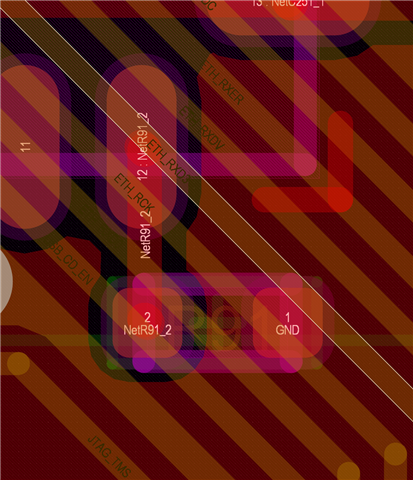

Cause was very small parasitic capacitance between RBIAS copper solder plane ant RGMII data lines planes at second layer. See picture:

To solve this problem need DE soldering chip and rbias resistor, isolate chip rbias contact, connect rbias copper plane to gnd(use as shield), and solder rbias 11k resistor directly to chip rbias contact and GND.

This tested and working Ok, but some difficult.

Possible light solution. Connect in parallels rbias resistor, 33pF capacitor. But not all noise avoid.

What can I use biggest capacitance? Is ok 0.1uF capacitor ?

I not found in application notes warnings about rbias sensitivity. Only - "rbias" must be close to chip.

Other problem I see with DP83869HM. This chip don't have ground pins, only pad. Pad must be connected to GND using via. So power coupling capacitors current must use vias.

Via have big impedance at high frequency.

What minimum via count and size must have pad connection with GND?

It seems to me that:

1. Rbias must have dedicated via to pad (avoid noise). Its true? Why rbias not included into chip?

2. Is quartz generator capacitors ground must have dedicated via to pad?

3. Which not used pins possible connect to pad ant GND? For better decoupling. To avoid vias (examp.: JTAG)

B.R.

Darius Babrauskas