Part Number: DS90UB953-Q1

Hi Expert,

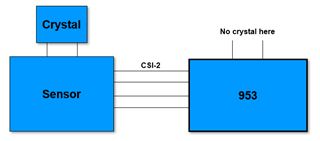

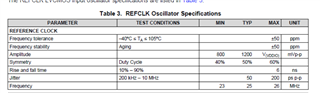

For the 953 and sensor connection, for one use case, if sensor use external clock from crystal X1 and 953 also use external clock from another crystal X2. The MIPI input clock from sensor to 953 is based on the crystal X1. for the 953, which clock will 953 use as reference clock ? crystal X2 or MIPI input clock from crystal X1?

Best regards,

Huang