Part Number: TLK2711-SP

Dear,sir

we are interface tlk2711 with fpga, we use GTXCLK . but we didn't received proper data which one we was transmitted.

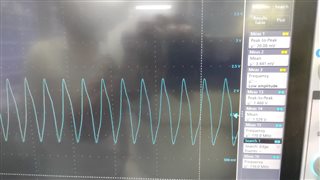

we have recevied data shown below.

| TKLSB | TKMSB | TX8-TX15 | TX0-TX7 | RX8-RX15 | RX0-RX7 |

| 0 | 1 | 0 | 0 | CB/F8 | C3/F0 |

| 0 | 1 | 0 | 1 | 8 | 0 |

| 0 | 1 | 0 | 2 | C9/1F | C9/1F |

| 0 | 1 | 0 | 3 | 8 | 0 |

| 0 | 1 | 0 | 4 | CA/9F | CA/9F |

| 0 | 1 | 0 | 5 | 4C | 0 |

| 0 | 1 | 0 | 6 | 8 | 0 |

| 0 | 1 | 0 | 7 | 8 | 0 |

| 0 | 1 | 0 | 8 | CC | CC |

| 0 | 1 | 0 | 9 | 8 | 0 |

| 0 | 1 | 0 | A | 8 | 0 |

| 0 | 1 | 0 | B | 8 | 0 |

| 0 | 1 | 0 | C | 8 | 0 |

| 0 | 1 | 0 | D | 8 | 0 |

| 0 | 1 | 0 | E | 8 | 0 |

| 0 | 1 | 0 | F | BC | B4 |

| 0 | 1 | 1 | 0 | FB | FB |

| ALL DATA IN HEX | |||||

so, we need to help from NI support, for decoding this sequences.