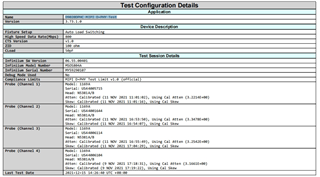

Part Number: SN65DPHY440SS

Hello:

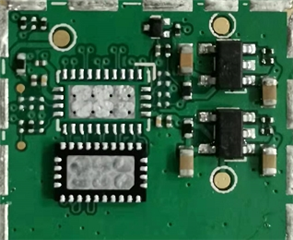

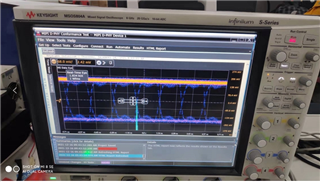

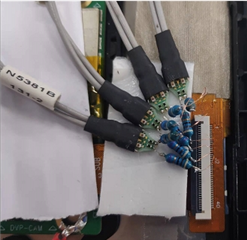

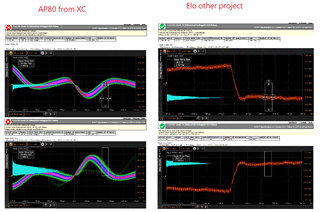

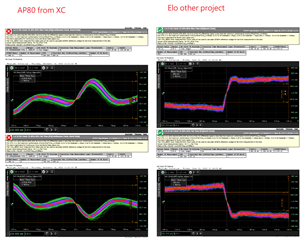

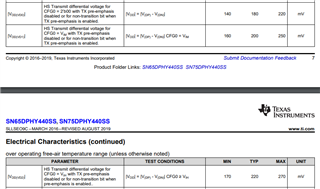

My client found that the analysis of d0231 auxiliary screen ESD problem is related to Mipi retimer ic-sn65dphy440ss and needs TI support,

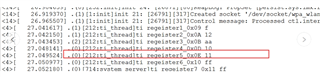

At this stage, the hard control scheme is adopted, later the soft control scheme needs to be verified, and My client wants TI to release the reference code, Thanks!!!