Part Number: TCA9803

Dear Specialists,

My customer is encountering transmission error at EMC test.

I would be grateful if you could advise.

---

TCA9803DGKR has a problem in the EMC test.

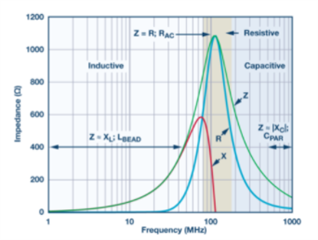

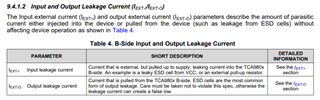

In the radiation immunity test, I2C error occurs when irradiating an electromagnetic wave of 10V / m at a frequency of about 80 to 100MHz.

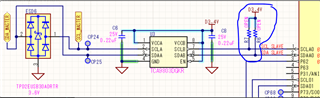

The circuit is attached PowerPoint. This connection was suggested by E2E.

TCA9803 connection diagram.pptx

The wiring distance between TCA9803s is roughly 30 cm to 50 cm.

The distance between TCA9803 to BUS MASTER and TCA9803 to SLAVE is within 10 cm.

I think that the wiring distance is long and it is affected by noise.

Could you please provide how to improve.

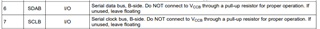

Is it better to use Pull Up or Pull Down at the receiving end when the transmitting distance is long?

---

I appreciate your great help in advance.

Best regards,

Shinichi