Part Number: DP83825EVM

I have taken two DP83825EVM boards and connected them back-back in unmanaged repeater mode but have so far been unable to get the setup to work.

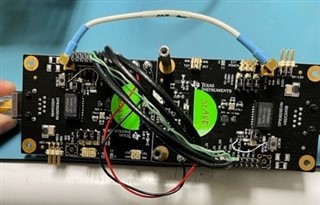

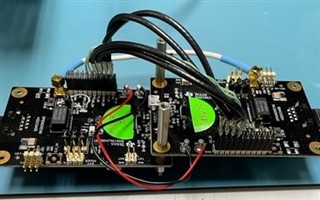

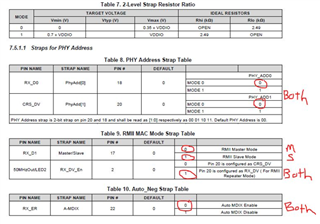

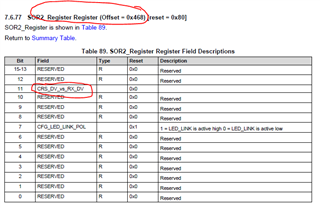

I painstakingly reconfigured the boards to do this even though the EVM is not exactly tailored well to support all of the needed jumper/strapping options specifically for repeater mode. Anyway, one is set up as master and the other as slave, mostly to make the clocking setup easier (feed 50MHz to slave from master and disconnecting slave's xtal). I connected the RMII signals with very short (3") pieces of coax for the cross-connected RX & TX signals. I have set the straps for repeater mode on both boards and slave mode (on the slave board), etc. I have set no registers, so all of them are default except for what the hardware straps configure.

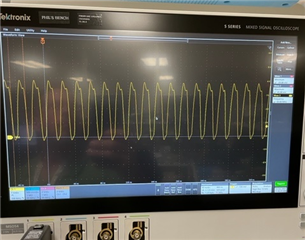

My test setup is simple. I connect the ethernet port from a Win 7 PC to one side of the repeater and another device (with fixed IP address) on the other side, then simply try to ping from PC to device. The device's interface is 10/100Base-T. Without the EVM boards in line, pinging works just fine but not with the board set in series. This whole setup is on a single bench top (short connection lengths). I can see each MDI side gets connected to at least some extent because when probing the TX and RX at the RJ45, I see the FLPs go away after CAT 5 is plugged in, indicating auto negotiation took place, plus activity lights stay on solid. When I send the pings, I see the activity lights on both EVM boards flash, indicating some activity. When I probe the RMII signals during pings from PC, I see data on the PC side (slave side) RX signals which connect to the TX pins on the device side (master) but never anything coming the other way. If I flip the board set (PC connected to master), I see the same thing. The 50MHz clock looks good/healthy (and is fed to from master to slave with coax). Since repeater mode is supposed to operate unmanaged, I even disconnected the MDIO signals going to the phy from the EVM's MCU, thinking perhaps some registers were getting set on power up. No help.

The EVMs are brand new but I did find a thread that talked about an older version of the die have XI and XO swapped, so I even tried moving the clock input to XO on the slave, definitely no help.

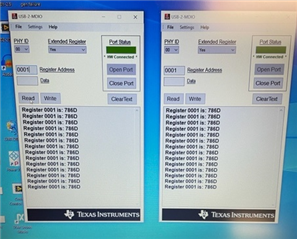

I have been unable to get the USB2MDI GUI, due to a driver loading problem (I have another thread started on this problem) so I have not been able to check any register settings.

Anyone have any thoughts on this? Are there any known bugs or hardware issues with these EVMs that has not been made public? I have scoured the forums but found nothing. I don't want to commit to using this chip in a design without seeing it work first.

Thanks,

Phil