Other Parts Discussed in Thread: ALP

HI,

Since lane rate supported by the deserializer is 400Mbps, 800Mbps and 1.6Gbps. Do we choose a lane rate that is higher than the required one. Say if we need 1.24Gbps (for 3840x2160@60, RAW10, 4 lanes), we have to choose 1.6Gbps in deserializer ?

On a related note, datasheet says we need to enable CSI skew calibration for 1.6Gbps lane rate. In case we have chosen 800Mbps lane rate. Will it send skew calibration sequence if enabled ?

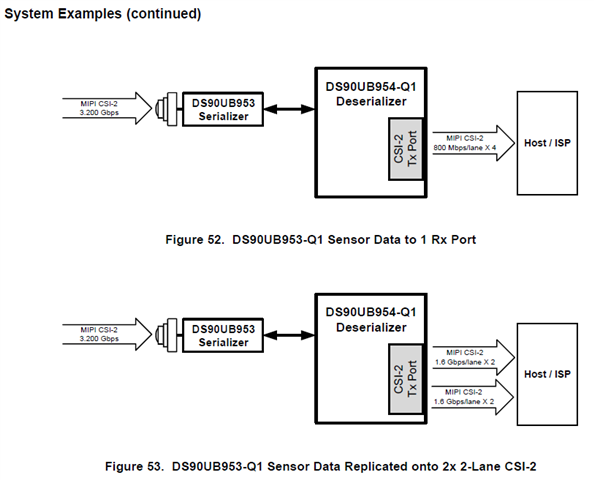

(click to enlarge)

(click to enlarge)