Other Parts Discussed in Thread: SN65LVCP23

Team,

My customer has a question.

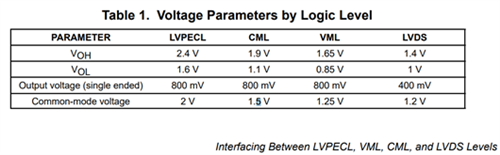

We are searching for a way to translate a 125Mbps LVDS differential signal from a POF (plastic optical fiber) transceiver (500-900mV differential output), to a LVPECL PHY input (800mV differential input minimum). These voltage ranges align with the below definitions of LVDS/LVPECL from TI’s app note. Note these are defined as single-ended.

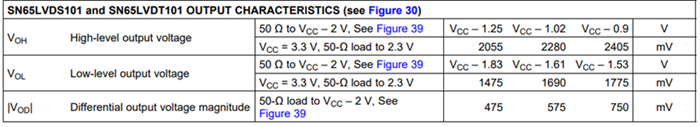

We are interested in TI’s SN65LVDx series of parts. However, I’m confused by the voltage ranges presented in the datasheet. I might be misunderstanding single ended vs. differential, etc. Why would a part claiming to have LVPECL output, give only up to 750mV differential output?

Can you shed some light for us?

Thanks,

Tom