What is the problem of concern if the capacitance of CVBUS2 is not implemented yet?

We would like to verify it on the actual machine and if there is no problem in this use case, we would like to unimplement it.

What kind of phenomenon will occur?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

What is the problem of concern if the capacitance of CVBUS2 is not implemented yet?

We would like to verify it on the actual machine and if there is no problem in this use case, we would like to unimplement it.

What kind of phenomenon will occur?

The capacitance is recommended to keep the VBUS clean (removing any noise). If the VBUS receives any jitter outside of the tolerances (typically +/0.5V) it could cause a disconnect/reset within the PD

Thank you for your reply.

"If the VBUS receives any jitter outside of the tolerances (typically ± 0.5V) it could cause a disconnect / reset within the PD"

How many pages in the datasheet do you have the details about?

What frequency fluctuation is "jitter"? VBUS2 applies the power of USB-PD.

Is there any problem if the USB-PD voltage does not fluctuate by ± 0.5V?

Could you please tell me in detail about the conditions for disconnect / resetting?

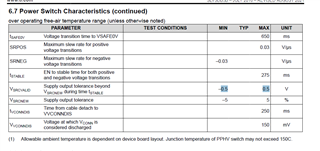

There is information in Table 6.7

This will answer any questions about the frequency of the jitter. There is no issue if it does not fluctuate. The conditions for disconnect/resetting depends on the PD role, the configuration, and the port partner. Either way it should be avoided and you can choose to not use a capacitor there at your own risk

Please see the datasheet here for more information: https://www.ti.com/lit/gpn/tps65988