Other Parts Discussed in Thread: DS90CF386

Hi team,

I used to post a I.mx8→941AS→928→DLPC230 issue:

Please see my update on the debug process:

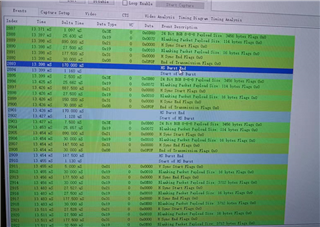

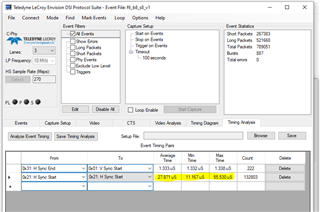

The mipi dsi event file (please open it with mipi software on computer)

dsi_events_f6_b8_s8_v1_20220218.zip

Customer also tested the SoC-941AS-928-DPLC120, with the same configuration the output is normal. But with DPLC230, it could not work and the DLPC230 fae said its timing requirement is more stricter than DLPC120.

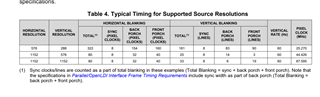

After cross-validation, we found that resolutions of 1152*576 and 864*480 can be lit on dlpc120, but not on dlpc230; this shows that dlpc230 has very strict timing requirements.

Did you see any successful experience with such combination with 1152*576@60hz resolution:

947+928+DLPC230;

941+928+DLPC230;

Could you please kindly provide us a proper timing for customer to set in SoC to let this resolution work properly?

We also analyzed the timing of 941 output, and found that the numbers of HAS, HFP and data in the last line are correct, but HBP has 35 more clocks (The number of Clocks that should be output theoretically is: 1152+8 + 50 + 40, the actual output is 1152+8+85+40)

Thank you!