Hi team,

As the title, can DSI85 support LVDS multi point to point? Thanks!

Jiawei

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

As the title, can DSI85 support LVDS multi point to point? Thanks!

Jiawei

Hi team,

Add one more question, just want to double check with you:

When resolution is 1962*1566*60, RGB888, the DSI CLK is 553MHz. Is it within DSI85 range?

Jiawei

Hi team,

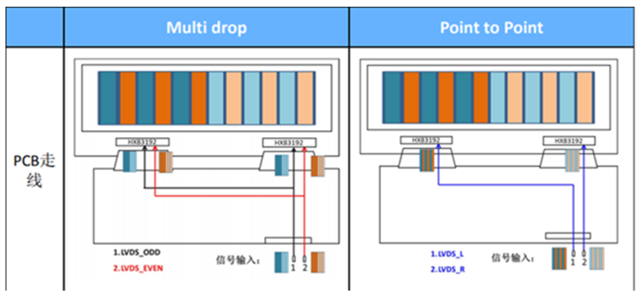

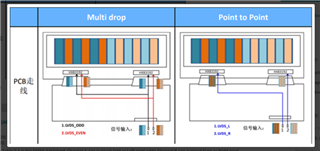

The multi point I say is like below, could you kindly support above questions? thanks!

Jiawei

Jiawei

DSI85 only supports point to point, it will not able to support multi point to point.

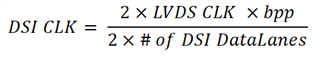

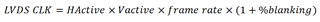

For LVDS CLK calculation, use the below formula

So the DSI CLK frequency = 663.66MHz, which is outside of the DSI85 max DSI clock frequency of 500MHz. So the DSI85 will not able to support this resolution.

Thanks

David

Hi David,

Thanks for your reply! Sorry for the misunderstanding expression. Let me clarify here:

Thanks!

Jiawei

Jiawei

So the DSI CLK = 2 * 92 * 24 / 2 * 8 = 276MHz and it is within the DSI85 reference clock supported range. You will use Channel A and B to drive the two LVDS.

Refer to Table 7-4 in the DSI85 datasheet, Channel A can support Odd or Left pixel while Channel B can support Even or Right pixel.

Thanks

David

Hi David,

From your reply, dsi8x selection is up to DSI CLK finally, right? I also want to check with you what is the meaning of 154M? Is 154M LVDS CLK single channel max or dual channel max pclk? From the selection e2e threat, DSI84 also supports the display from lvds pclk side, it is really confusing.

Moreover, could you give more comments on channel a can support left while channel b can support right pixel? Does it mean dsi8x support the left application of above figure? Does it mean dsi8x support multi drop?

Thanks and look forward you reply!

Jiawei

Jiawei

Since DSI84 is a single DSI channel (4 DSI lanes), then the DSI CLK calculation will be DSI CLK = 2 * 92 * 24 / 2 * 4 = 552MHz, outside the DSI CLK frequency range, so the DSI84 will not able to support this panel.

Can you share the panel spec? I don't see it being attached to this e2e thread.

Thanks

David

Jiawei

So where did this diagram come from as I don't see it in the panel datahsheet.

But the DSI85 can only point to point, it can't support multi drop connection.

Thanks

David

Hi David,

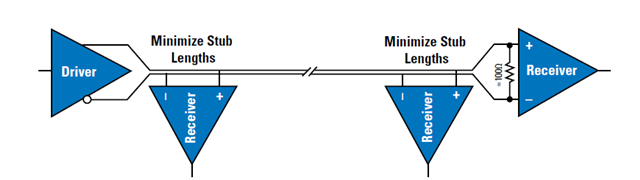

A lot of customer said there are many high resolution display is multi drop structure, and they have used DSI8x driver display successfully. I also asked FPD-LINK BU, like 948 also said 948 support multi drop, but need to pay attention stubs length and PCLK range.

Can you explain why DSI8X can't support multi drop? Also because of the stub?

Thanks!

Jiawei

Jiawei

The DSI8x LVDS output was not designed to support multi-drop LVDS implementation. You can possibly add buffer as a possible solution, but then you have to take the skew of the buffer into the system design consideration.

Thanks

David