Part Number: DP83826E

Other Parts Discussed in Thread: AM5708,

Hello TI Experts,

I'm currently working on a custom board from a customer, I try to get DP83826 working on the board.

The PHY is connected to an AM5708 with RMII signals. Straps are configured to have RMII Master by default, looks good on this point.

Basic device tree and other linux configuration already done and double checked.

Problem: I haven't any Link when connecting to the local network, whatever I'm connected to a switch or direct to my computer. Link up with loopback cable ok.

Trying to follow Ethernet Debug Guide at e2e.ti.com/.../Ethernet-Debug-Techniques.pdf, here is the checklist:

- Verify resistances:

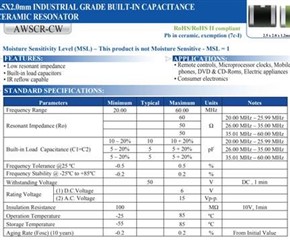

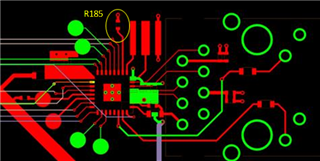

RBIAS is 6.49k

No resistances on RMII signals between the PHY and the AM5708 (not sure it's really nice but don't know the impacts....)

- Verify magnetic connection

Looks good

- Verify power rails:

VDD and VDDIO ok

RBIAS voltage seems floating near 0V => This is not normal but I don't know how to fix it !!

- Verify X1 clock:

25MHz ok

- Verify strap pins:

Looks good

- Probe TD+/- signal

With 100ohms terminated cable, I see the pulse

- Connection of loopback RJ45 cable:

Working, Link is up in kernel logs !!!!

- Registers:

Basic Mode Control Register (BMCR) Register Address 0x00h => 0x3100 => 100Mbps, AutoNegociation, Full-Duplex

Basic Mode Status Register (BMSR) Register Address 0x01h => 0x7849 => No link established

Auto-Negotiation Advertisement Register (ANAR) Register Address 0x04h => 0x01E1

Auto-Negotiation Link Partner Ability Register (ANLPAR) Register Address 0x05h => 0xCDE1

PHY Status Register (PHYSTS) Register Address 0x10h => 0x4102 => Seems to indicate MDI swapped (I'm connected to my computer so looks good) but at 10Mbps and Half Duplex only. Not sure how to interpret this...

Don't know where to go now and would sincerely appreciate any ideas that may go in the right direction for this problem !

Regards,

Joel

EDIT: after a while, registers 0x10 value is 0x5102, seems to indicate an inverted polarity but I don't know what the datasheet is speaking about (which polarity it is).