Part Number: DS90UB960-Q1

Hi team,

My customer has encountered an issue of 935-960.

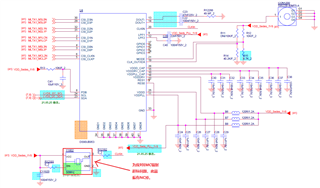

DS90UB960 connects three DS90UB953, in them two cameras are in synchronous mode, and another one uses an external clock in asynchronous mode. The camera in the external clock asynchronous mode is dropping frames. Will it be a problem to use this way?