Part Number: DS90UB948-Q1

Other Parts Discussed in Thread: ALP, USB2ANY

Hi

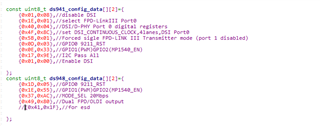

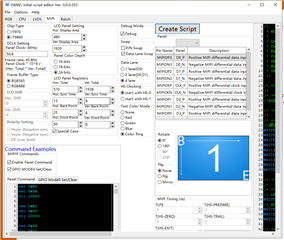

I am now troubleshooting which part of the video output has a problem. SER:941 DES:948 Now I want to output pattern from 948. My configuration is as follows:

WriteOfI2c_Byte(UB948,0x49,0x80);//SET MODE_SEL0

WriteOfI2c_Byte(UB948,0x1D0x05);

WriteOfI2c_Byte(UB948,0x1E,0x55);

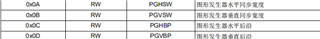

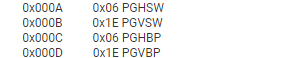

WriteOfI2c_Byte(UB948,0x66,0x03); //enable PGCDC1

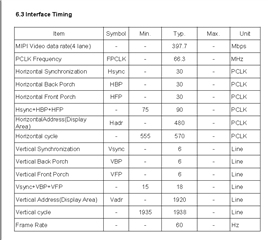

WriteOfI2c_Byte(UB948,0x67,0x03); //66.6M pclock

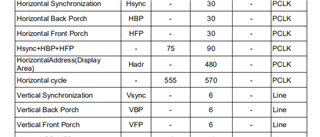

//H V 1920*480

WriteOfI2c_Byte(UB948,0x66, 0x07);

WriteOfI2c_Byte(UB948,0x67,0x80);

WriteOfI2c_Byte(UB948,0x66,0x08);

WriteOfI2c_Byte(UB948,0x67,0x07);

WriteOfI2c_Byte(UB948,0x66,0x09);

WriteOfI2c_Byte(UB948,0x67,0x1E);

//H V TOTAL 1938*570

WriteOfI2c_Byte(UB948,0x66,0x04);

WriteOfI2c_Byte(UB948,0x67, 0x92);

WriteOfI2c_Byte(UB948,0x66,0x05);

WriteOfI2c_Byte(UB948,0x67,0xA7);

WriteOfI2c_Byte(UB948,0x66,0x06);

WriteOfI2c_Byte(UB948,0x67,0x23);

//HBP: 14

WriteOfI2c_Byte(UB948,0x66,0x0C);

WriteOfI2c_Byte(UB948,0x67,0x0E);

//VBP: 6

WriteOfI2c_Byte(UB948,0x66,0x0D);

WriteOfI2c_Byte(UB948,0x67,0x06);

//H SYNC 13

WriteOfI2c_Byte(UB948,0x66,0x0A);

WriteOfI2c_Byte(UB948,0x67,0x0D);

//V SYNC 6

WriteOfI2c_Byte(UB948,0x66,0x0B);

WriteOfI2c_Byte(UB948,0x67,0x06);

WriteOfI2c_Byte(UB948,0x66,0x0E);//enable PBSC

WriteOfI2c_Byte(UB948,0x67, 0x03); /set negtive

WriteOfI2c_Byte(UB948,0x65,0x03); //enable 24bit and internal clock

WriteOfI2c_Byte(UB948,0x64,0x11); //enable pattern generator

I write 941's 0x01 register WriteOfI2c_Byte(UB941, 0x01, 0X08); to close 941's dsi. Make sure not to affect the 948 output pattern.

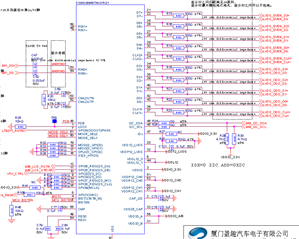

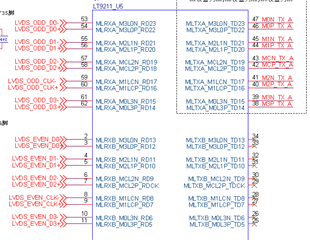

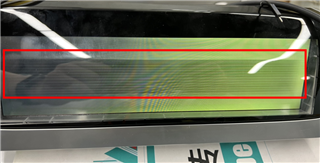

but The latter lvds to mipi signal chip cannot recognize the lvds signal and the clock detected by the two signals is 16468, which should be 32300.

what's the problem? Are there any other registers that are not configured?Or my thinking is wrong?

thanks