Other Parts Discussed in Thread: ALP

Hi,

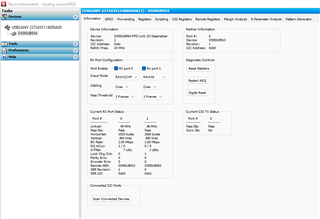

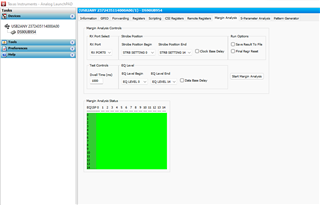

I am running the MAP tool on a 913/954 fpd link and see that all EQ and SP positions are being marked as passed. I assume this should not be the case and something is wrong as the FPD-link cable is ~5m and I would expect some positions to fail. I have attached the info page and MAP tab to see if something is wrong.

Kind Regards