Hi,TI

The design block diagram refers to the PDF:

I2S: 32bit; LRCK:48KHz; BCLK: 6.144MHz

The MCLK outputs 12.288MHz via 948

941 register setting:

| address | value |

| 0x12 | 0x0b |

| 0x10 | 0x77 |

| 0x11 | 0x77 |

| 0x1a | 0x00 |

948 register setting:

| address | value |

| 0x20 | 0x55 |

| 0x21 | 0x55 |

| 0x2b | 0x01 |

| 0x3a | 0xb1 |

The problem that arises now is that the output is unstable I2S_SDO on the 948 side.

When the 948-side I2S waveform is OK, after restarting the system again, the waveform may appear NG phenomenon, and the I2S_SDO has no output. At NG, there is an SDO signal on the 941 side.

Based on this situation, what is your company's advice.

1.Is the register set correct?

2.I2S_SDI can be transferred remotely from the 948 to the 941?

3.Do registers set timing requirements?

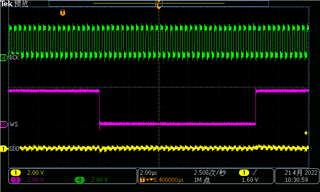

OK:

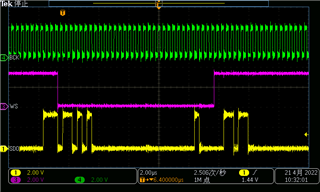

NG: