Part Number: TMDS181

Hi Team,

can you please help with the topic below:

We are a manufacturer of digital training systems by means of uncompressed video transmission to numerous participants in a room in real time. It is not uncommon for the video signal to have to be transmitted over longer distances.

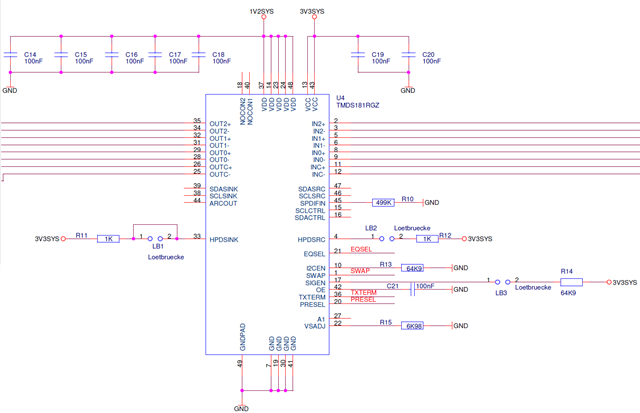

For this reason, we have chosen to further develop new 4K-capable products when choosing a retimer for your TMDS181. So far, we are very satisfied with the performance of this component in our first prototypes.

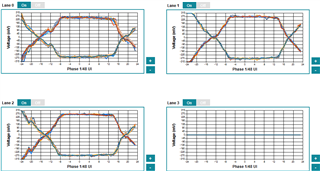

However, we noticed during the cascading of several retimers that the image signal becomes unstable and has sporadic dropouts. As a result, posts in official TI forums may be due to a jitter that is growing increasingly from retimer to retimer.

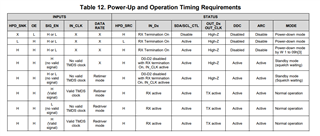

To be able to analyze this in more detail, our hardware developer would like to read it out using I²C and evaluate the EyeDiagram. Among other things, this is generated by parameters, which can only be found in an extended data sheet/manual according to the TI Forum. In addition to register bank 0 , the register bank 1 ( > HX20 registers) of the parameterization I²C bus is to be explained, which is not included in the free downloadable data sheet.

We would be very pleased if you could support us in this, in order to realize your product in cascades.