Hi Team,

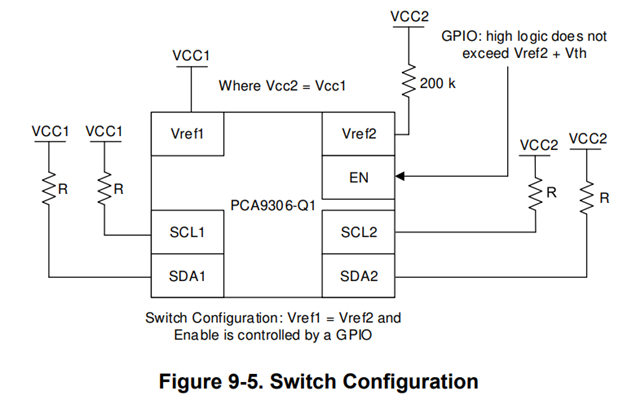

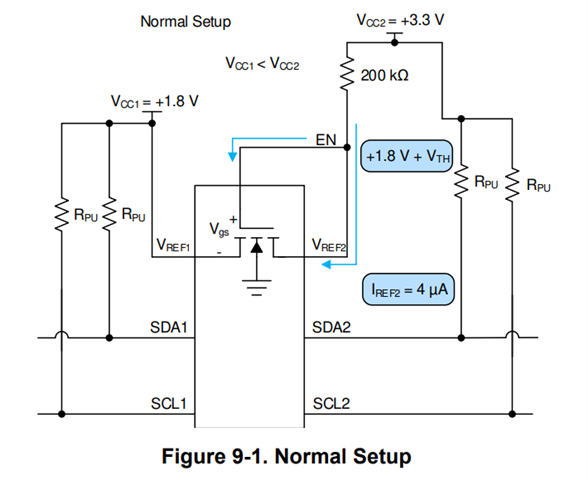

My customer is using PCA9306-Q1 as an I2C switch while VREF1=VREF2=1.8V. I have a question about the voltage selection of EN pin. Why we can't choose high logic to exceed Vref2+Vth? My understanding is that this will help reduce the Rds(on) of internal FET. In such condition(VREF1=VREF2=1.8V), there will not be too much current flowing between VREF1 and VREF2.

What is the purpose of internal FET between VREF1 and VREF2? Is it used for start-up only? There're also extra two FETs between SDA1&SDA2/SCL1&SCL2 right?

BR,

Oliver Tang