Other Parts Discussed in Thread: SN65DSI86

Hi TI engineers,

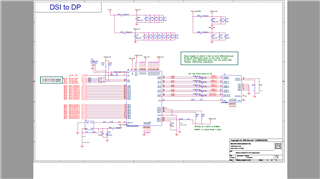

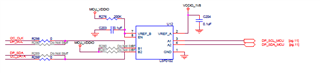

I have encountered one issue during using SN65DSI86. I found that the I2C bus of DSI86 was broken. The SCL is always driven to GND by DSI86 which will block I2C bus to send any command. I even can't send out command to the good devices hooked together with DSI86. Only after removing DSI86, I can send out I2C command. So in which case will the DSI86 SCL pin be short to GND?

thanks and best regards,

chaodong