Part Number: DP83869HM

Other Parts Discussed in Thread: DP83869

Hi,

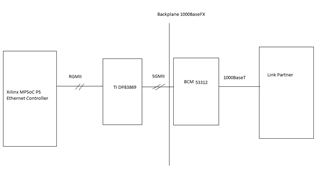

We are using DP83869 chip in RGMII-SGMII mode. Block diagram is attached for your reference. RGMII is connected to MAC of XILINX MPSoC PS and the SGMII

interface goes via backplane to the ethernet switch (BCM53312). We are not able to achieve the communication from the board to LP.

Following experiments were carried out.

1. On writing REG(0xC00) = 0x0140 the link status is detected. On trying to ping, we could observe the packets reaching at the LP (using wireshark).

On further assessing at the switch, we could see that the packets were arriving at the SW from LP but wasn't reaching the Xilinx MPSoC MAC. Are we missing anything to be configured at 1000BaseFX side?

2. We have followed the register dumps mentioned in the link https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1080094/dp83869hm-dp83869-in-rgmii-sgmii-mode-does-not-work-at-100m?tisearch=e2e-sitesearch&keymatch=RGMII%2525252520to%2525252520SGMII%2525252520bridge# but couldn't achieve much.

3. We forced 1000Mbps at Xilinx-MAC, TI PHY(Both RGMII and SGMII side), BCM53312 to Copper. There's no luck.

Would you please let us know if anything else can be tried?