Other Parts Discussed in Thread: TS3DV642,

Hi

Customer has a question currently using the combination of SN65DP159 + TS3DV642

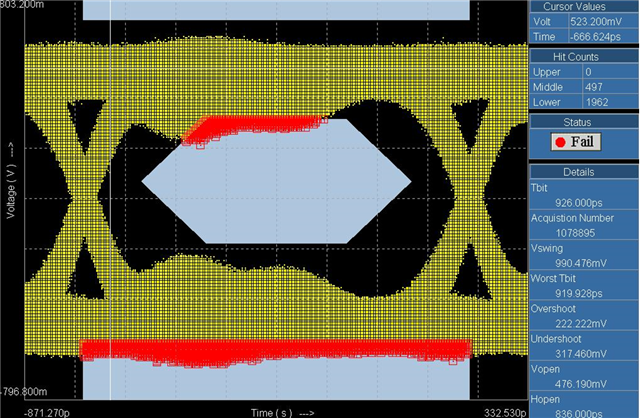

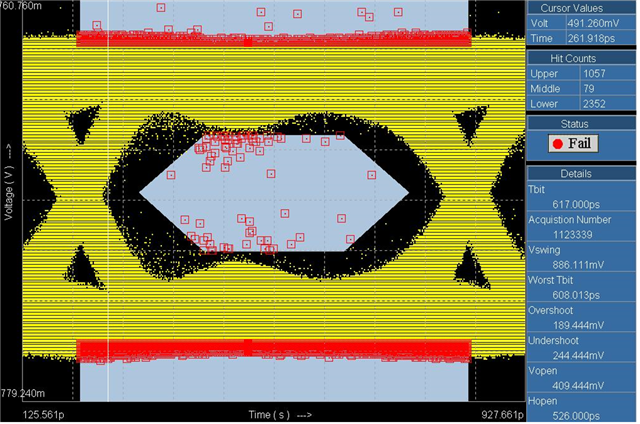

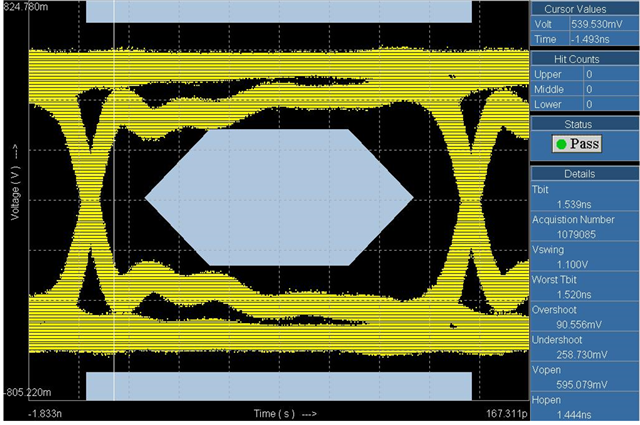

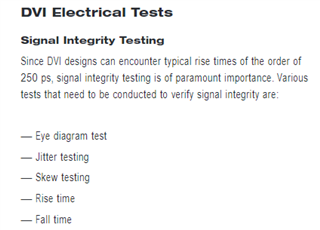

DVI SI measurement eye diagram Fail (as attached)

Are there any suggestions?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

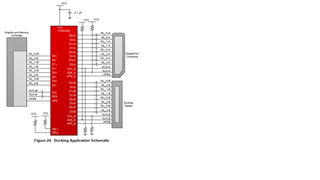

Can you please share your schematic, layout and current DP159/TS3DV642 configuration?

Thanks

David

Hi David

Thank you for your support

Please refer the attachment

We’ll modify HDMI(DVI) layout diff impedance from 85ohm to 100ohm next version.

At this moment, is there any other setting to improve our SI ?

Hi,

Is there a way to change the design so you can have the DP159 on the output of TS3DV642? With the TS3DV642 between the DP159 output and the HDMI connector, you need to use the DP159 TX Pre-emphasis and Vsadj to compensate for the loss between the TS3DV642 loss and the output trace insertion loss.

But even if the eye diagram can be improved with the TX Pre-emphasis and Vsadj, the differential impedance test may still fail because the Ron with the TS3DV642.

Thanks

David

Hi David

Is there a way to change the design so you can have the DP159 on the output of TS3DV642?

IS there any difference between our design to SPEC ?

Is this layout impedance correct ?

Hi,

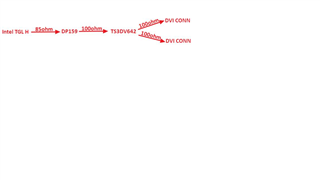

The layout impedance is correct. Is it possible to go with a topology like this

Intel TGL -> TS3DV642 -> DP159 -> DVI connector

-> DP159 -> DVI connector

Thanks

David

Hi David

If don’t have enough PCB space to place additional DP159.

Which the SMB source is to connect DP159 PCH or EC ?

Do we have to set I2C control status every time when system boot up ?

Is the test fail result could be fixed after we change the impedance next stage ?

Thanks

Hi,

If don’t have enough PCB space to place additional DP159.

*** Can you place DP159 at the output of TS3DV642, Intel TGL -> TS3DV642 -> DP159 -> DVI connector.

Which the SMB source is to connect DP159 PCH or EC ?

*** Can you please clarify this question, I am not sure what you mean.

Do we have to set I2C control status every time when system boot up ?

*** If any I2C register values are changed from the default value, then you will need to reprogram them after power up

Is the test fail result could be fixed after we change the impedance next stage ?

*** I don't think the impedance will solve this issue. You can change the DP159 Pre-emphasis or Vsadj and see if the issue can be fixed. But even with the eye diagram fixed by tuning the DP159 Pre-emphasis or Vsadj, you may still fail the differential impedance compliance test.

Thanks

David

Hi David

If don’t have enough PCB space to place additional DP159.

*** Can you place DP159 at the output of TS3DV642, Intel TGL -> TS3DV642 -> DP159 -> DVI connector.

Which the SMB source is to connect DP159 PCH or EC ?

*** Can you please clarify this question, I am not sure what you mean.

Do we have to set I2C control status every time when system boot up ?

*** If any I2C register values are changed from the default value, then you will need to reprogram them after power up

Is the test fail result could be fixed after we change the impedance next stage ?

*** I don't think the impedance will solve this issue. You can change the DP159 Pre-emphasis or Vsadj and see if the issue can be fixed. But even with the eye diagram fixed by tuning the DP159 Pre-emphasis or Vsadj, you may still fail the differential impedance compliance test.

Thank you

Hi,

Can you use the topology as shown below?

Intel TGL -> TS3DV642 -> DP159 -> DVI connector

-> DP159 -> DVI connector

Thanks

David

Hi,

For DVI compliance testing, it looks the following is checked. The differential impedance compliance testing associated with HDMI is not checked. So the concern I had with TS3DV642 Ron does not apply here.

For the eye diagram test, have you tried to change the DP159 pre-emphasis and Vsadj to see if they help?

Thanks

David