Other Parts Discussed in Thread: ALP, USB2ANY

Dear expert,

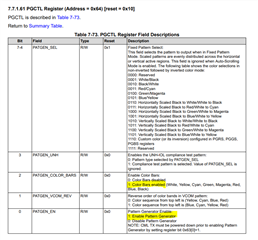

In UB948 datasheet, CML_OUTPUT_CTL3 register "CML TX must be powered down prior to enabling Pattern Generator."

Why there is this requirement? My customer never do this but Pattern Generator is still OK.

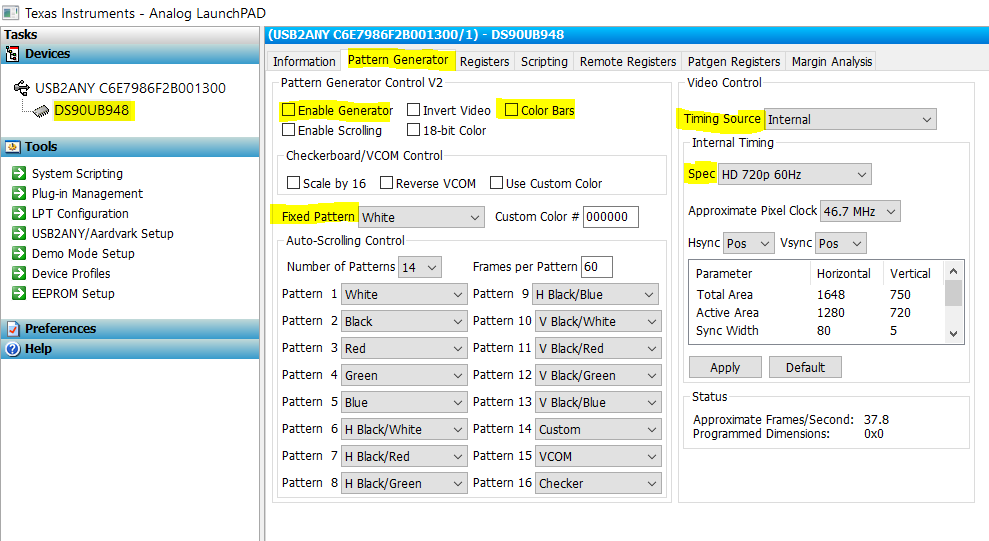

In 7.3.16 Internal Pattern Generation, "Enabling PATGEN on the DS90UB948-Q1, using the internal clock, will cause loss of communication between the serializer and deserializer, so internal PATGEN from the DS90UB948-Q1 should only be enabled via local I2C access."

What does this mean?

One of my customer A use UB941 to configure UB948 pattern. Pattern works fine and LOCK is stable during pattern.

My another customer B use UB941 to configure UB948 pattern, they see unlock after 0x64 bit 0 to Enable Pattern Generator and there is no output at screen.

They use the same pattern configure. The main difference is customer A has both external reference clock and DSI clock valid. Customer B 's board is new board who don't have external reference clock and DSI clock is not present. So we use internal reference clock to debug first. Does it make difference? And that's why there is no output at screen?

Thanks