Hi TI Team,

We want to generate the bin(EEPROM) file from the SigCon architect tool, because we did some changes(CH3 lane reversal & raw data output) to the low-level page. So, I request you that share the procedure.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi TI Team,

We want to generate the bin(EEPROM) file from the SigCon architect tool, because we did some changes(CH3 lane reversal & raw data output) to the low-level page. So, I request you that share the procedure.

Hi Sathish,

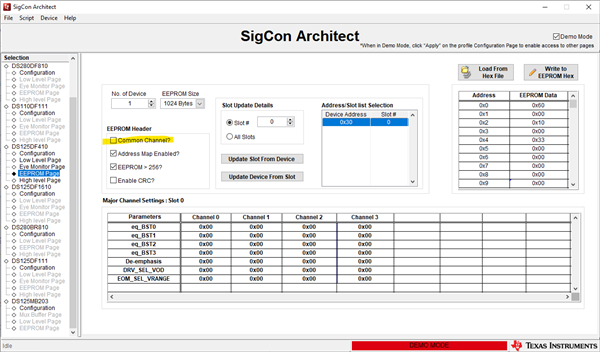

After making changes to the low level page or high level page in SigCon Architect, you can select "update slot from device" in the EEPROM page. This will update the EEPROM settings with the latest device settings that have been configured in SigCon Architect. After verifying that the changes look appropriate, you can select "write to EEPROM hex" to generate a hex file in the Intel hex file format.

Thanks,

Drew

Hi Drew,

We did the changes on low level page and followed the above your instructions, and generated hex file. After flashing the bin file to EEPROM, changes are not replicating. So, Let's share your feedback if we are missing any settings.

CH3

Add Default // we want bit 7 high for inverting the polarity(0xD5)

0x1F 0X55

Thanks,

Sathish.

Hi Sathish,

Apologies for not catching this sooner. Since this setting is only being applied to a single channel, you will need to disable "common channel" on the EEPROM page.

Common channel enables the device to save EEPROM space by using the same settings for each channel. Since this is not suitable for your use case, this must be disabled.

Thanks,

Drew