Hi team,

One of our customer's issues, I'm forwarding it below, could you please provide some troubleshooting suggestions

In actual use, the customer found that when the video was output of 1280*720p_yuv422_8bit@30fps, the DS90UB960-Q1 would output 4 additional columns of data for a total of 1284*720 data.

The above problem still exists when using the DS90UB960-Q1 test pattern.

The test mode initialization code is as follows:

0x32,0x01, //CSI0 select

0x33,0x03, //CSI_EN & CSI0 2Lane,BIT[5:4] controls lane count

0x21,0x83, // replicate port 0 to port 1

0x20,0x00, //e0//forwarding of RX0 to CSI0

0x1f,0x02,

0x4c,0x01,//

0x6E,0xAA, //BC_GPIO_CTL0: FrameSync signal to GPIO0/1

0x10,0x91,

0x58,0x58, //enable pass throu BCC_CONFIG Register:BACK Channel config

//0x19,0x01, //FS_HIGH_TIME_1

//0x1A,0x15, //FS_HIGH_TIME_0

//0x1B,0x09, //FS_LOW_TIME_1

//0x1C,0xc2, //FS_LOW_TIME_0

//0x18,0x01, //Enable FrameSync

//0x19,0x01, //FS_HIGH_TIME_1

0x1A,0x06, //FS_HIGH_TIME_0

0x1B,0x5b, //FS_LOW_TIME_1

0x1C,0x9b, //FS_LOW_TIME_0

0x18,0x43, //Enable FrameSync

//0x1f,0x02,

0x6d,0x7f, //Configure port to coax mode and FPD III to CSI mode

0x5c,0xb0, //7-bit Remote Serializer Alias ID TX_ID

0x5d,0x60, //7-bit Remote Slave Device ID 0 Sensor ID

//Sensor physical ID

//Configures the physical I2C address of the remote I2C Slave device

//attached to the remote Serializer. If an I2C transaction is addressed

//to the Slave Alias ID3, the transaction is remapped to this address

//before passing the transaction across the Bi-directional Control

//Channel to the Serializer.

0x65,0x60, //7-bit Remote Slave Device Alias ID 0 Sensor Alias ID

//Configures the decoder for detecting transactions designated for an

//I2C Slave device attached to the remote Serializer. The transaction

//is remapped to the address specified in the Slave ID0 register. A

//value of 0 in this field disables access to the remote I2C Slave.

0x70,0x1e, //RAW10_datatype_yuv422b10_VC0

0x7c,0xe1,

0xB0,0x00,

0xB1,0x01,

0xB2,0x01,

0xB1,0x02,

0xB2,0x33,

0xB1,0x03,

0xB2,0x1e,//yuv8bit

0xB1,0x04,

0xB2,0x0a,//1280*2

0xB1,0x05,

0xB2,0x00,

0xB1,0x06,

0xB2,0x01,

0xB1,0x07,

0xB2,0xE0,

0xB1,0x08,

0xB2,0x02,

0xB1,0x09,

0xB2,0xD0,

0xB1,0x0A,

0xB2,0x04,

0xB1,0x0B,

0xB2,0x1A,

0xB1,0x0C,

0xB2,0x0C,

0xB1,0x0D,

0xB2,0x67,

0xB1,0x0E,

0xB2,0x21,

0xB1,0x0F,

0xB2,0x0A,

0x20,0x00, //e0//forwarding of RX0 to CSI0

-------------------------------------------------------------

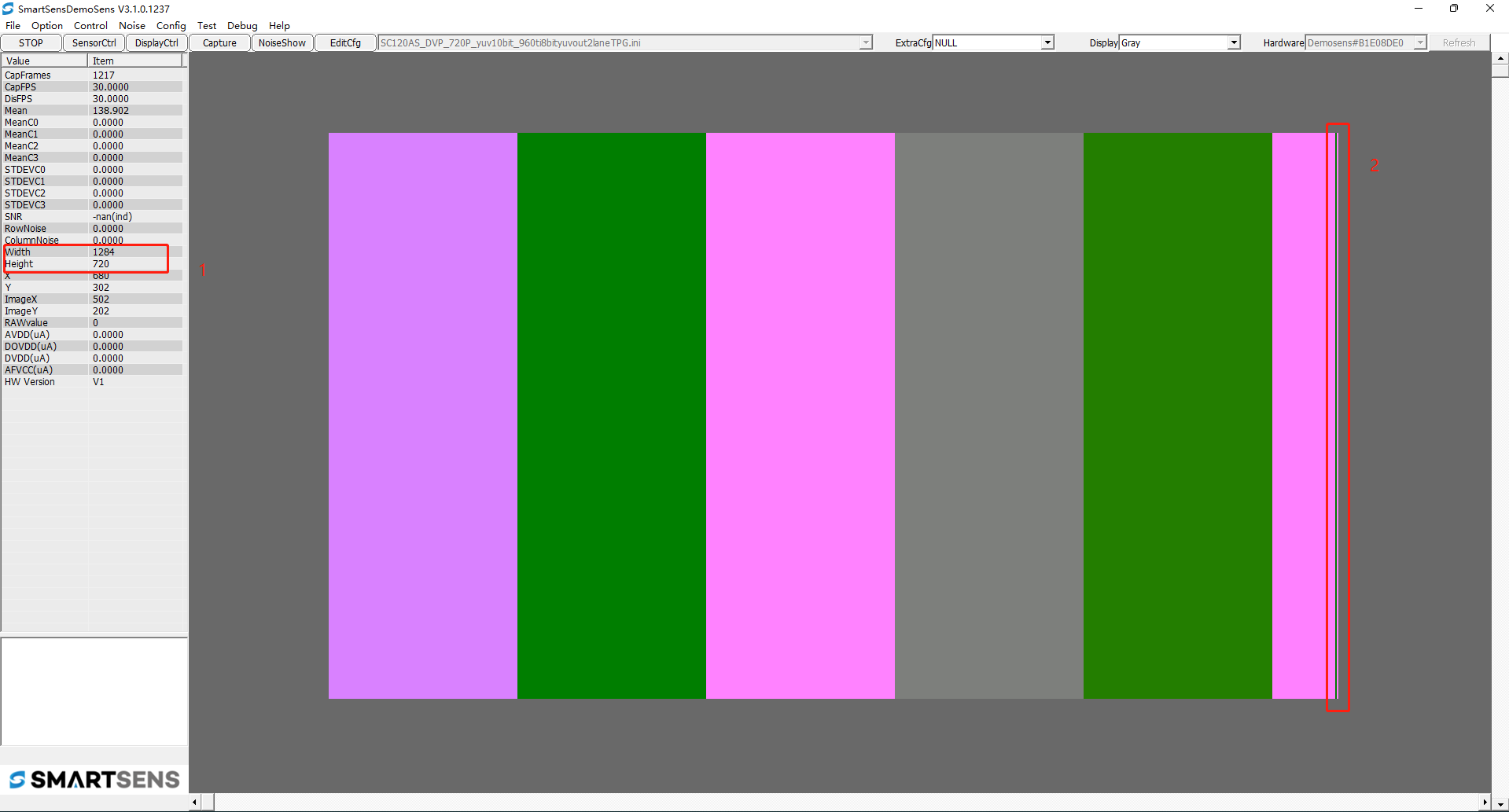

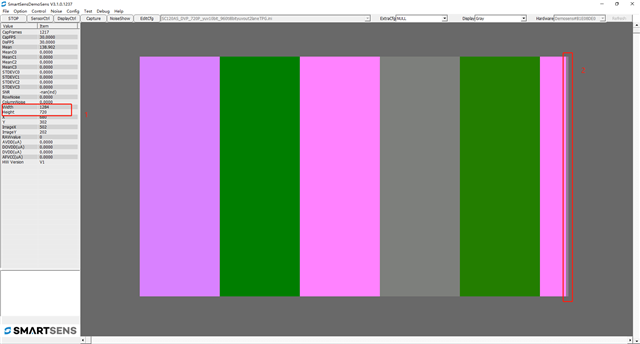

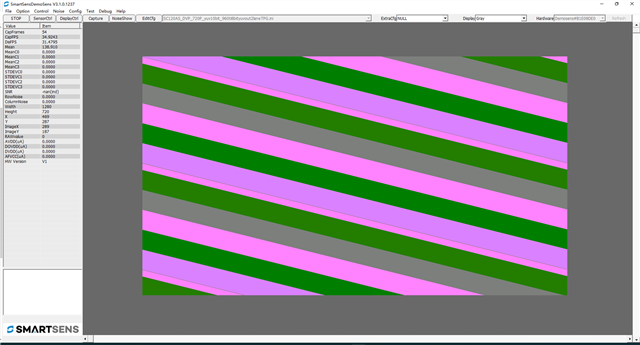

As the code shows, the configured test mode output is yuv4228bit of 1280*720.However, the upper computer software must be configured to 1284*720 parse the image to get a correct image, and there is a noticeable column of anomalies to the right of the image, as shown in the following figure.

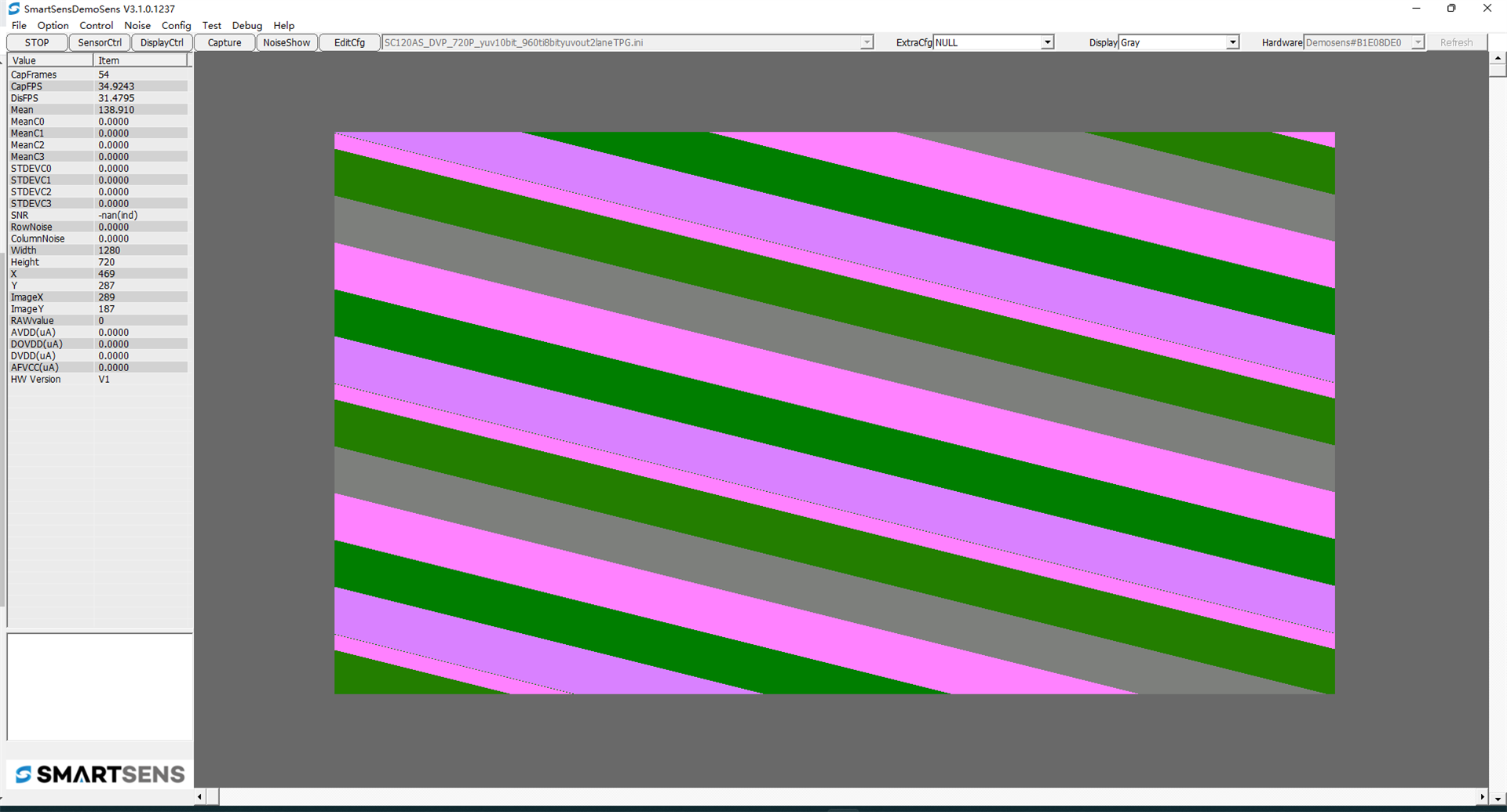

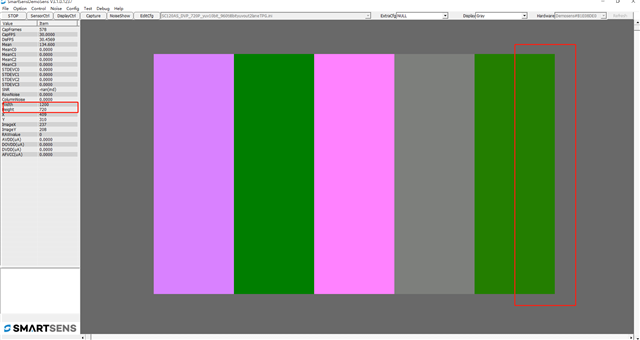

If I use 1280 * 720 to resolve, I get an image like this:

What's more interesting is that I'm adjusting the test pattern output data to a yuv output of 1200x720, and that's not the problem.The code changes are as follows

0x32,0x01, //CSI0 select

0x33,0x03, //CSI_EN & CSI0 2Lane,BIT[5:4] controls lane count

0x21,0x83, // replicate port 0 to port 1

0x20,0x00, //e0//forwarding of RX0 to CSI0

0x1f,0x02,

0x4c,0x01,//

0x6E,0xAA, //BC_GPIO_CTL0: FrameSync signal to GPIO0/1

0x10,0x91,

0x58,0x58, //enable pass throu BCC_CONFIG Register:BACK Channel config

//0x19,0x01, //FS_HIGH_TIME_1

//0x1A,0x15, //FS_HIGH_TIME_0

//0x1B,0x09, //FS_LOW_TIME_1

//0x1C,0xc2, //FS_LOW_TIME_0

//0x18,0x01, //Enable FrameSync

//0x19,0x01, //FS_HIGH_TIME_1

0x1A,0x06, //FS_HIGH_TIME_0

0x1B,0x5b, //FS_LOW_TIME_1

0x1C,0x9b, //FS_LOW_TIME_0

0x18,0x43, //Enable FrameSync

//0x1f,0x02,

0x6d,0x7f, //Configure port to coax mode and FPD III to CSI mode

0x5c,0xb0, //7-bit Remote Serializer Alias ID TX_ID

0x5d,0x60, //7-bit Remote Slave Device ID 0 Sensor ID

//Sensor physical ID

//Configures the physical I2C address of the remote I2C Slave device

//attached to the remote Serializer. If an I2C transaction is addressed

//to the Slave Alias ID3, the transaction is remapped to this address

//before passing the transaction across the Bi-directional Control

//Channel to the Serializer.

0x65,0x60, //7-bit Remote Slave Device Alias ID 0 Sensor Alias ID

//Configures the decoder for detecting transactions designated for an

//I2C Slave device attached to the remote Serializer. The transaction

//is remapped to the address specified in the Slave ID0 register. A

//value of 0 in this field disables access to the remote I2C Slave.

0x70,0x1e, //RAW10_datatype_yuv422b10_VC0

0x7c,0xe1,

0xB0,0x00,

0xB1,0x01,

0xB2,0x01,

0xB1,0x02,

0xB2,0x33,

0xB1,0x03,

0xB2,0x1e,//yuv8bit

0xB1,0x04,

0xB2,0x09,//1280*2

0xB1,0x05,

0xB2,0x60,

0xB1,0x06,

0xB2,0x01,

0xB1,0x07,

0xB2,0xE0,

0xB1,0x08,

0xB2,0x02,

0xB1,0x09,

0xB2,0xD0,

0xB1,0x0A,

0xB2,0x04,

0xB1,0x0B,

0xB2,0x1A,

0xB1,0x0C,

0xB2,0x0C,

0xB1,0x0D,

0xB2,0x67,

0xB1,0x0E,

0xB2,0x21,

0xB1,0x0F,

0xB2,0x0A,

0x20,0x00, //e0//forwarding of RX0 to CSI0

--------------------------------------------------------------------

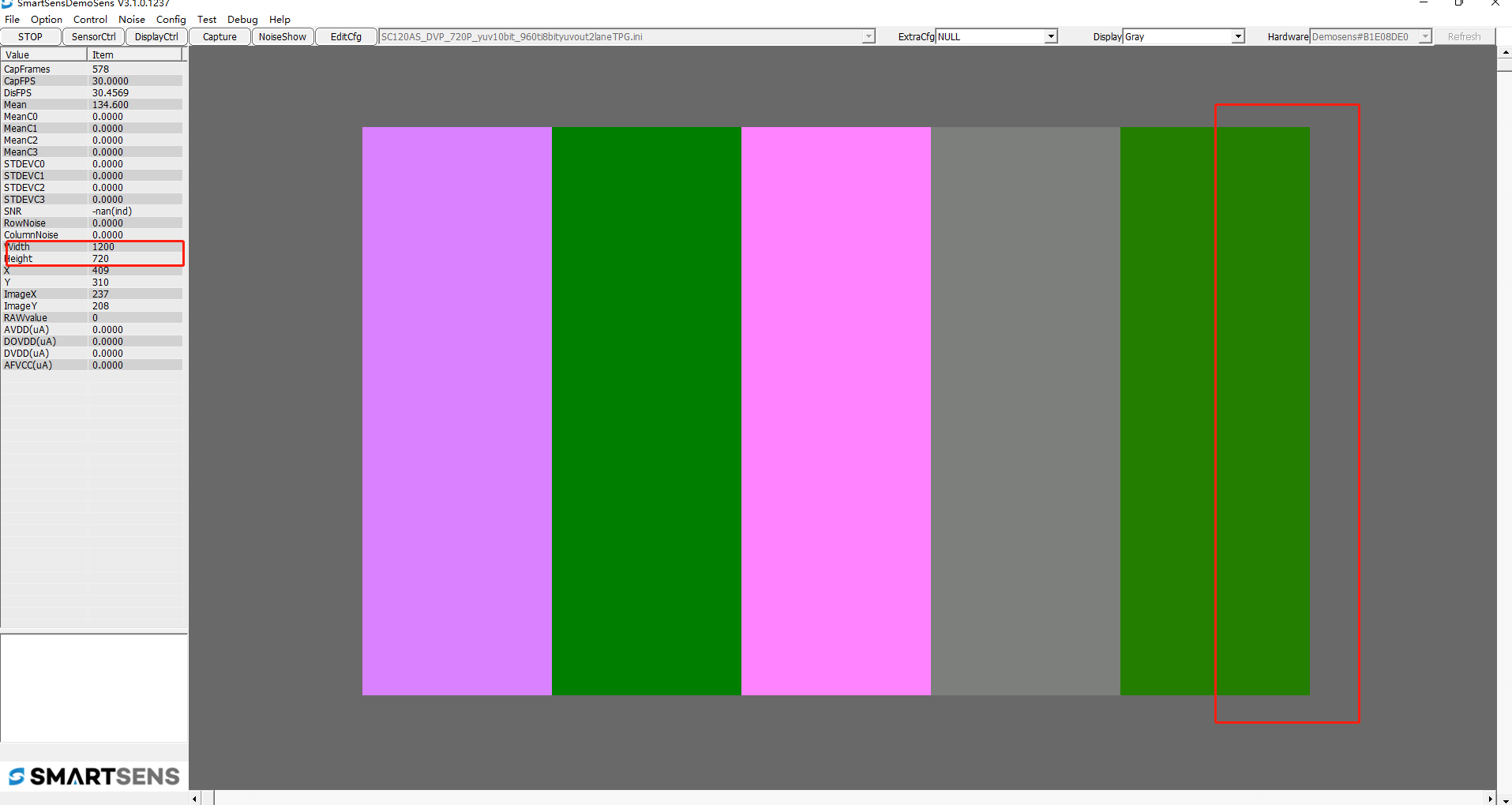

The plot is as follows, the right side of the image is not abnormal and is parsed correctly at the set resolution.

The register values for DS90UB960-Q1 under test pattern mode are as follows:

0x0,0x7a,

0x1,0x00,

0x2,0x1e,

0x3,0x40,

0x4,0xd0,

0x5,0x01,

0x6,0x00,

0x7,0xfe,

0x8,0x1c,

0x9,0x10,

0xa,0x7a,

0xb,0x7a,

0xc,0x0f,

0xd,0x09,

0xe,0x01,

0xf,0xff,

0x10,0x91,

0x11,0x00,

0x12,0x00,

0x13,0x00,

0x14,0x00,

0x15,0x00,

0x16,0x00,

0x17,0x00,

0x18,0x43,

0x19,0x00,

0x1a,0x06,

0x1b,0x5b,

0x1c,0x9b,

0x1d,0x00,

0x1e,0x04,

0x1f,0x02,

0x20,0x00,

0x21,0x83,

0x22,0x00,

0x23,0x00,

0x24,0x00,

0x25,0x00,

0x26,0x00,

0x27,0x00,

0x28,0x00,

0x29,0x00,

0x2a,0x00,

0x2b,0x00,

0x2c,0x00,

0x2d,0x00,

0x2e,0x00,

0x2f,0x00,

0x30,0x00,

0x31,0x00,

0x32,0x01,

0x33,0x03,

0x34,0x00,

0x35,0x01,

0x36,0x00,

0x37,0x01,

0x38,0x00,

0x39,0x00,

0x3a,0x00,

0x3b,0x00,

0x3c,0x00,

0x3d,0x00,

0x3e,0x00,

0x3f,0x00,

0x40,0x00,

0x41,0xa9,

0x42,0x71,

0x43,0x01,

0x44,0x00,

0x45,0x00,

0x46,0x20,

0x47,0x00,

0x48,0x00,

0x49,0x00,

0x4a,0x00,

0x4b,0x12,

0x4c,0x01,

0x4d,0x13,

0x4e,0x04,

0x4f,0x1a,

0x50,0x13,

0x51,0x00,

0x52,0x00,

0x53,0x00,

0x54,0x00,

0x55,0x00,

0x56,0x00,

0x57,0x00,

0x58,0x58,

0x59,0x00,

0x5a,0x00,

0x5b,0xb2,

0x5c,0xb0,

0x5d,0x60,

0x5e,0x00,

0x5f,0x00,

0x60,0x00,

0x61,0x00,

0x62,0x00,

0x63,0x00,

0x64,0x00,

0x65,0x60,

0x66,0x00,

0x67,0x00,

0x68,0x00,

0x69,0x00,

0x6a,0x00,

0x6b,0x00,

0x6c,0x00,

0x6d,0x7f,

0x6e,0xaa,

0x6f,0x88,

0x70,0x1e,

0x71,0x2c,

0x72,0xe4,

0x73,0x00,

0x74,0x00,

0x75,0x00,

0x76,0x00,

0x77,0xc5,

0x78,0x00,

0x79,0x01,

0x7a,0x00,

0x7b,0x00,

0x7c,0xe1,

0x7d,0x00,

0x7e,0x00,

0x7f,0x00,

0x80,0x00,

0x81,0x00,

0x82,0x00,

0x83,0x00,

0x84,0x00,

0x85,0x00,

0x86,0x00,

0x87,0x00,

0x88,0x00,

0x89,0x00,

0x8a,0x00,

0x8b,0x00,

0x8c,0x00,

0x8d,0x00,

0x8e,0x00,

0x8f,0x00,

0x90,0x00,

0x91,0x00,

0x92,0x00,

0x93,0x00,

0x94,0x00,

0x95,0x00,

0x96,0x00,

0x97,0x00,

0x98,0x00,

0x99,0x00,

0x9a,0x00,

0x9b,0x00,

0x9c,0x00,

0x9d,0x00,

0x9e,0x00,

0x9f,0x00,

0xa0,0x00,

0xa1,0x00,

0xa2,0x00,

0xa3,0x00,

0xa4,0x00,

0xa5,0x1a,

0xa6,0x00,

0xa7,0x00,

0xa8,0x00,

0xa9,0x00,

0xaa,0x00,

0xab,0x00,

0xac,0x00,

0xad,0x00,

0xae,0x00,

0xaf,0x00,

0xb0,0x00,

0xb1,0x0f,

0xb2,0x0a,

0xb3,0x08,

0xb4,0x25,

0xb5,0x00,

0xb6,0x18,

0xb7,0x00,

0xb8,0xfb,

0xb9,0x33,

0xba,0x83,

0xbb,0x74,

0xbc,0x80,

0xbd,0x00,

0xbe,0x00,

0xbf,0x00,

0xc0,0x00,

0xc1,0x00,

0xc2,0x00,

0xc3,0x00,

0xc4,0x00,

0xc5,0x00,

0xc6,0x00,

0xc7,0x00,

0xc8,0x00,

0xc9,0x00,

0xca,0x00,

0xcb,0x00,

0xcc,0x00,

0xcd,0x00,

0xce,0x00,

0xcf,0x00,

0xd0,0x00,

0xd1,0x43,

0xd2,0x94,

0xd3,0x02,

0xd4,0x60,

0xd5,0xf2,

0xd6,0x00,

0xd7,0x02,

0xd8,0x00,

0xd9,0x00,

0xda,0x00,

0xdb,0x00,

0xdc,0x00,

0xdd,0x00,

0xde,0x00,

0xdf,0x00,

0xe0,0x00,

0xe1,0x00,

0xe2,0x00,

0xe3,0x00,

0xe4,0x00,

0xe5,0x00,

0xe6,0x00,

0xe7,0x00,

0xe8,0x00,

0xe9,0x00,

0xea,0x00,

0xeb,0x00,

0xec,0x00,

0xed,0x00,

0xee,0x00,

0xef,0x00,

0xf0,0x5f,

0xf1,0x55,

0xf2,0x42,

0xf3,0x39,

0xf4,0x36,

0xf5,0x30,

0xf6,0x00,

0xf7,0x00,

0xf8,0x00,

0xf9,0x00,

0xfa,0x00,

0xfb,0x00,

0xfc,0x00,

0xfd,0x00,

0xfe,0x00,

0xff,0x00,

Best Regards,

Amy Luo