Hi TI Team,

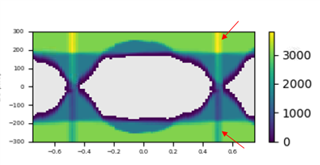

We tried to plot the eye diagrams in heatmap format and noticed higher than normal BER during bit transition. It does not seem to make sense. Can you explain to us why this happens? Is it normal and expected?

Thanks.

Child

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi TI Team,

We tried to plot the eye diagrams in heatmap format and noticed higher than normal BER during bit transition. It does not seem to make sense. Can you explain to us why this happens? Is it normal and expected?

Thanks.

Child

Hi Child,

Can you clarify how you are determining the heat map? Are you simply looking at the hit count? below for reference is the methodology suggested by TI.

I'm not used to seeing the signature that you are observing when plotting the retimer input eye. This observation should be don't care though, as it is happening at high error region of the eye diagram anyways.

Thanks,

Rodrigo Natal

Hi Rodrigo,

I think we are talking about the same method, except that we have higher resolution for the color map. The color map from Table 53 may not show what we see, because any points with BER >1000 will be coded RED. Any idea?

Thanks.

Child

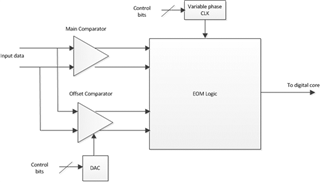

I believe this signature you are observing is a result of the retimer eye opening monitor (EOM) methodology. See EOM functional description below. The EOM comparators delta is max at the eye crossing. I think theoretically that is the result you would want see.

Regards,

Rodrigo Natal

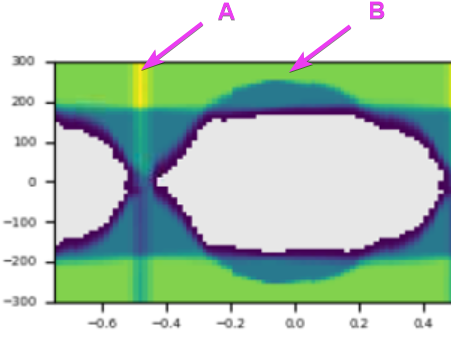

Rodrigo,

Thanks for the additional details of how the EOM works. However, by principle, the following two spots (A and B) should have the same bit error hits because their error rates should be 50% (half of the bits coming in are ONEs which are discriminated as ZEROs, as the threshold voltage of the comparator at A and B is high enough to make no difference in detected error rates)

Is the chip spending the same amount of time to record bit error hits at A and B? If it happens to spend more time at A, we will see higher bit error hits at A. But is it the case?

Thanks.

Child

Yes, EOM spends equal amount of time for areas A and B.

Regards,

Rodrigo Natal

Hi Child,

Please allow me to look into this question. I can provide an update later today.

Thanks,

Drew

Hi Child,

After further investigation, I don't have a great explanation as to why area A has a higher hit count than area B. With that said, is this impacting your ability to interpret data from the EOM?

Thanks,

Drew

Drew,

We do want to know why that happens because it seems to have revealed some internal issues and we would like to confirm if such an issue is predictable and limited (to certain conditions). Can your team dig deeper into the root cause?

Thanks.

Child

Hi Child,

I'm working with our team to look deeper into the root cause. I can provide an update on Monday.

Thanks,

Drew

Hi Child,

I am still waiting to hear back from a teammate regarding the root cause of this. I will update you later this week on this.

Thanks,

Drew