Other Parts Discussed in Thread: ALP

Hi Team,

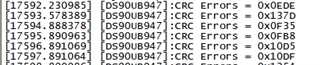

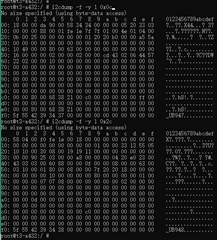

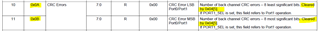

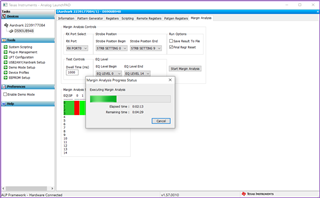

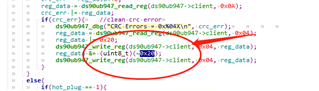

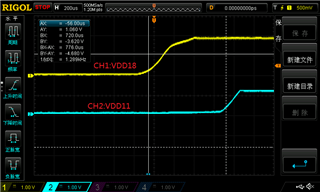

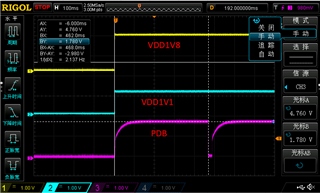

We have another issue:some panel will touch carton,I2C transparent transmission failure with high probability, our engineer already read the 0x0A/0x0B registers of 947 and found many number of back channel CRC errors.

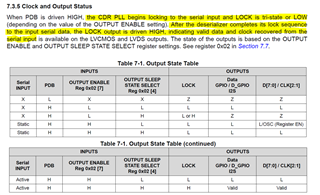

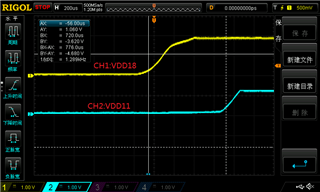

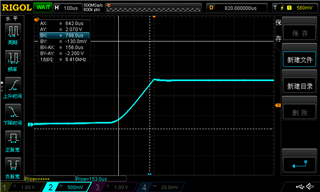

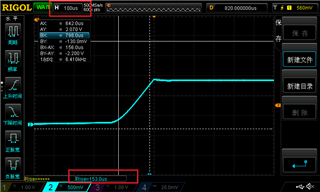

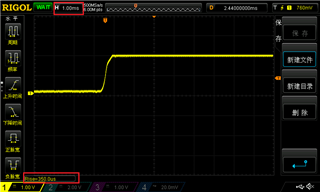

Try to use oscilloscope to measure the 948, the lock single is clear,without any pulses and low level.

We had do som AB swap, it following with 947.

We check the datasheets of 947 and 948, it does not have any describes of back channel, so can you give us some suggestion about this issue?

Best Regards!