Hello and thank you for taking time to help me with my confusion i really appreciate it.

I am designing a HDMI to LVDS bridge using a HDMI to DVI (TFP401APZP) and then a DVI to LVDS (SN65LVDS93AIDGGRQ1). The schematic using both can be seen in the attached PDF.6332.Schematics.pdf

The settable pins on the SN65LVDS93AIDGGRQ1 are as follows:

Output Power Down = 3.3V

Staggered Pixel Select = 3.3V

Pixel CLK Setting = GND

Output Drive Strength = GND

Power Down = 3.3V

ODCK Format = GND

ODCK Polarity = 3.3V

I am having difficulties with getting the HDMI source (My computer) to begin transferring visual data to the PCB (all of the differential pairs are completely still). I have tied together the Hot-Plug detect to the 5V provided by the HDMI source to indicate that there is a device present with no effect. (There should be a 1k resistor between the pins however i didnt have room to solver since the pins are so close together - though i dont believe this should be an issue)

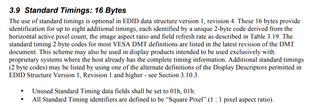

After then doing some more reading I came to the conclusion that its the DDC/EDID requirement not being fulfilled. This is where i meet my problem of, how do I encode and communicate the TFT data so that when the HDMI is plugged in the resolution and other necessary parameters are transmitted? Am i correct it this deduction?

Do I need to use some I2C Eeprom connected to pin 15 & 16 on the HDMI connector with the PC providing the I2C clock to begin communication?

The DVI output from the first chip is then connected to SN65LVDS93AIDGGRQ1 that outputs an LVDS signal to the TFT.

The TFT i am using is attached below: its a 10" 1024 x 768

I will continue to do some reading, I'm at the point where i dont know what else could be causing the issue.

Thank you once again for your help, i really look forward to learning what I'm missing.

Best Regards,

Kacper