Part Number: DS90UH941AS-Q1

Other Parts Discussed in Thread: DS90UB928Q, ALP, USB2ANY

Hi team,

One of our customer's issues, I'm forwarding it below, could you please provide some guidance?

Scenario:

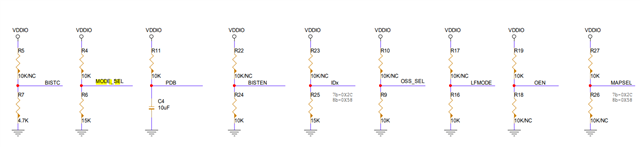

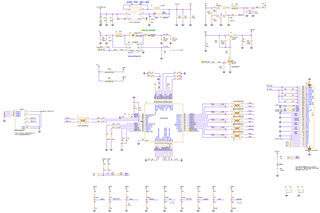

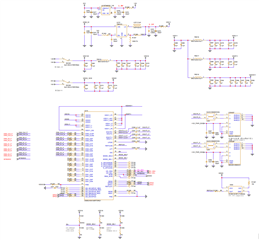

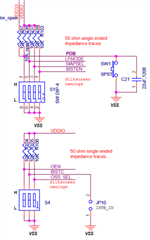

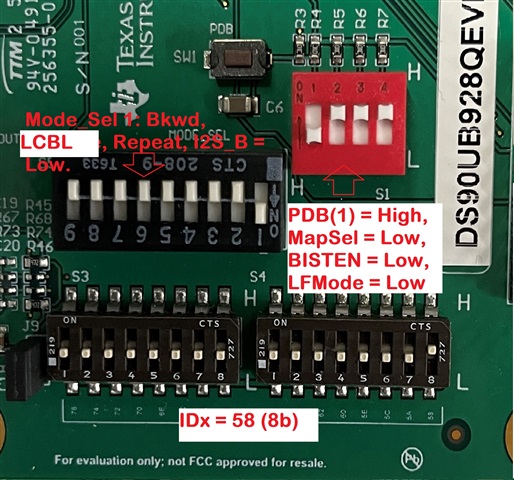

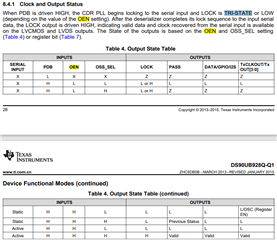

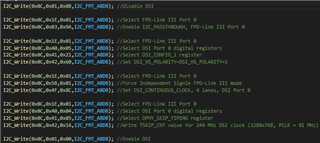

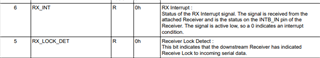

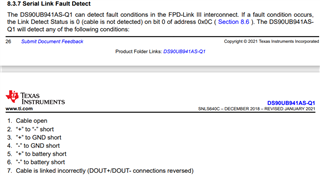

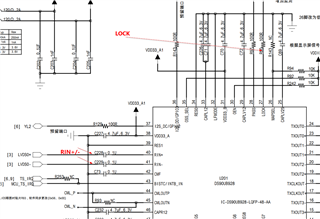

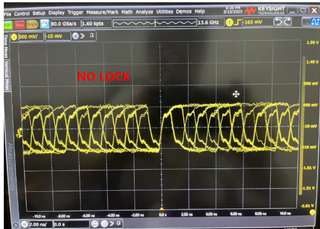

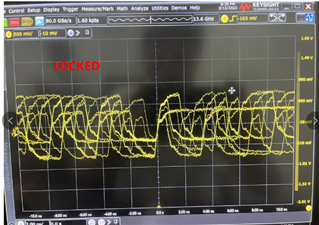

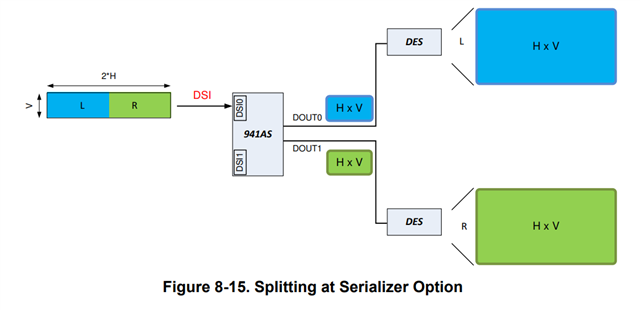

Enter 2560x768 stitching RGB888 data to DS90UH941AS-Q1 using one MIPI DSI4lane and divided into two serial signals of 1280x768 via the internal splitter, each of which is input into two DS90UB928Q.It is deserialized and converted into LVDS signals, which are output to two LVDS panels respectively. As shown in the following figure of the datasheet.

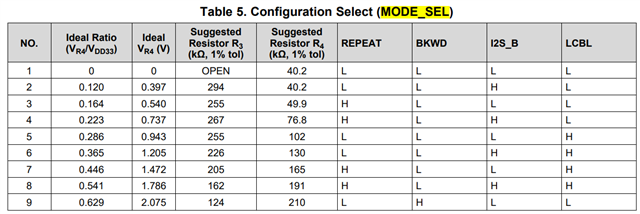

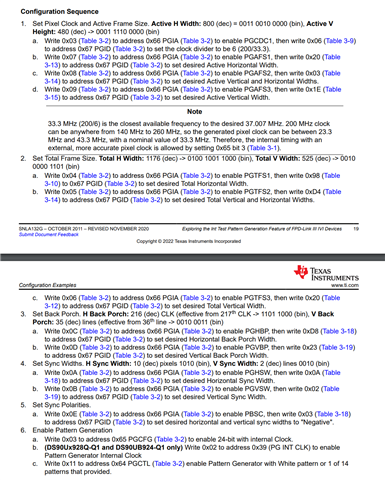

1, MIPI DSI two 1280x768 splice not complete, can 941AS Pattern generator generate two 1280x768 serial signal output for debugging screen use?

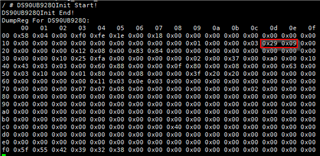

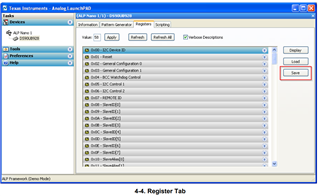

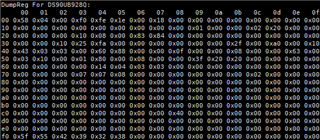

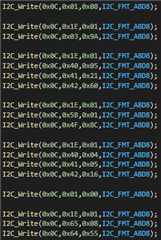

2, 941AS and 928Q, are there tools to generate a list of initialization parameters that meet the power-up timing requirements?

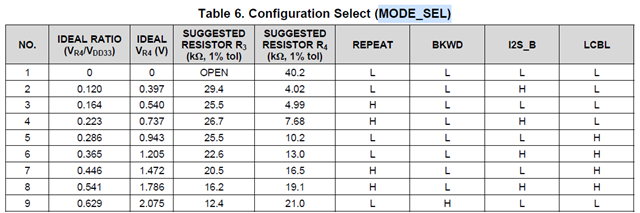

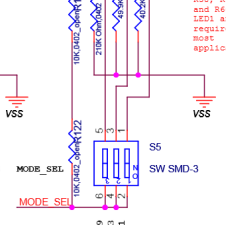

3, whether the LVDS screen needs to be illuminated by 2:2 single pattern first, how to configure the initialization parameters of 941AS and 928Q

Best Regards,

Amy Luo