Hello,

My thread this time is related to my previous thread shown below.

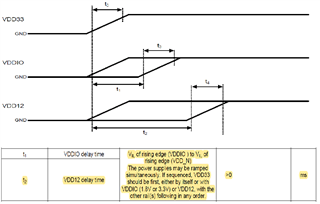

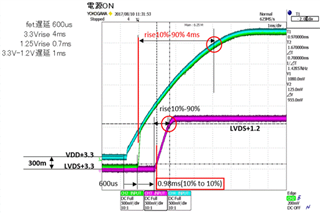

My customer checked their existing system which was designed based on the power up sequence shown in revision A. They controlled VDD12 to start rising after VDD33 at 10% voltage level as shown below. However the sequence has changed in revision D or between A and D which may violate the new requirement because VDD12 rose before VDD33 at 90% voltage level. Would you please tell me if it does?

Best Regards,

Yoshikazu Kawasaki