Hi TI Team,

We have been playing with the EOM_TIMER_THRx registers by changing the threshold value from the default 0x30 to other higher values. The datasheet said it could go all the way to 0xff. However, we found that the maximum value has to be lowered in order to read out the EOM error counts properly. Are there any other considerations to increase the threshold value?

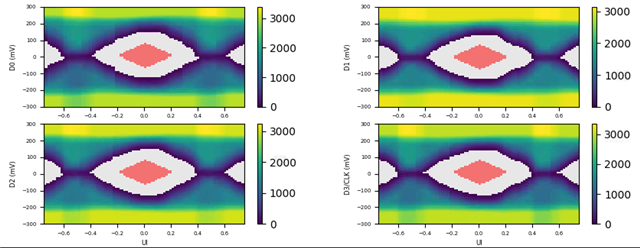

Case 1: 6Gbps, Reg 0x2a = 0x30 (default value)

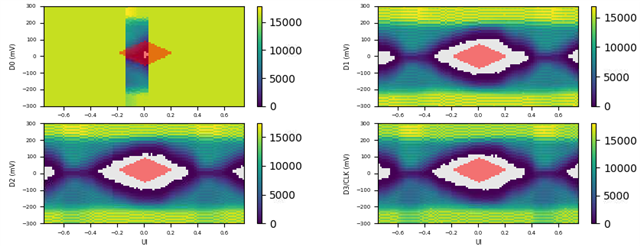

Case 2: 6Gbps, Reg 0x2a = 0xff

When we set 0x2a to 0xff, the error count readout is wrong (with channel 0). Is that what we should expect? Why?

Thanks.

Child