Other Parts Discussed in Thread: TS3DV642

Hello,

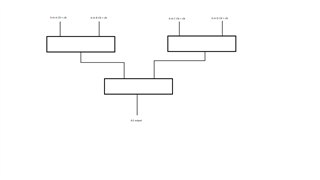

I am designing a test board that requires a variety of throughput signals, but the one I'm struggling with is the MIPI CSI. I have four cameras that need to be tested, but only enough hardware to have one input. My current idea is to use a multiplexer, and it seems only 2:1 multiplexers exist for 10+ channels. Because I need to test four different 4 channel CSI signals, my thought is to use three 2:1 multiplexers in a cascade configuration. If this is unfeasible or there is a better way, I am all ears.

This is my rudimentary block diagram of how I think it could work.

Thank you in advance.