Part Number: SN65LV1224B

Other Parts Discussed in Thread: SN65LV1023A

Hello,

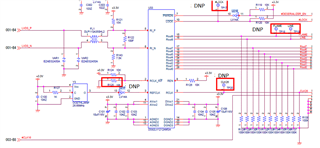

My customer has unlock issue on SN65LV1224B after replacing from DS92LV1212A(They didn't have any unlock issues at all when they had used DS92LV1212A). My customer's system is similar to the following thread except they use MT9V034 and 26.66MHz clock.

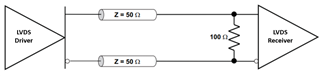

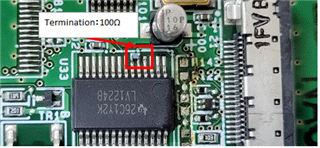

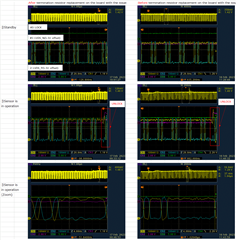

They have unlock issue depending on the boards. If they probe the LVDS lines, they don't see unlock issue, but if they leave the lines unprobed, they do unlock issue. Would you please tell me how they should do for fixing the unlock issue? Can they add some capacitors on the lines? If so, how big capacitors they can add? Note that they confirmed the REFCLK is within +/-100ppm. Note also that they removed the PU/PD resistors at the LVDS lines.

1.Power on the system -> /LOCK=Lo -> Normal operation

2.System in standby mode -> /LOCK=Lo -> Normal operation

3.System goes to operational mode -> /LOCK=Hi -> Abnormal operation

4.Probing the LVDS lines -> /LOCK=Lo -> Normal operation

5.Leaving the LVDS lines unprobed -> /LOCK=Hi -> Abnormal operation

Best Regards,

Yoshikazu Kawasaki