Ethernet design at 100M Base-T,6 pruduct samples put in the temperature chamber for testing. Say them as #1,#2,#3,#4,#5,#6.

Step 1. At +25℃, Ethernet port could operate normally for all 6 samples.

Step 2. At -20℃, #3 ethernet port could operate normally.

#1,#2,#4,#5,#6 ethernet port can't communicate with computer. with yellow LED on constantly, and green LED quick flashing

Step 3. Interchage the chip DP83822IRHBR from #3 and #4.

Step 4. At +25℃, Ethernet port could operate normally for #3 and #4.

Step 5. At -20℃, #4 ethernet port could operate normally.

#3 ethernet port can't communicate with computer. with yellow LED on constantly, and green LED quick flashing

Question: If the chip have any concern in low ambient temperature?

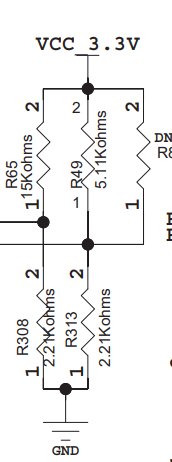

Attached is my schematic