Part Number: DP83867CS

Other Parts Discussed in Thread: DP83867E

Hi Team,

When my customer did compliance test of their DP83867CSRGZR board under 10Base-Te, the compliance test results became as follows,

I would appreciate any advice on their compliance test results.

In addition, the results are the same as the e2e test results below.

1.e2e URL

e2e.ti.com/.../dp83867ir-10base-te-100base-tx-1000base-t-compliance-test

2.10Base-Te Test results

- 2 fails at the following items,

1) TP_IDL Template, with TPM (last bit CD0) : Fail at Load2

2) TP_IDL Template, with TPM (last bit CD1) : Fail at Load2

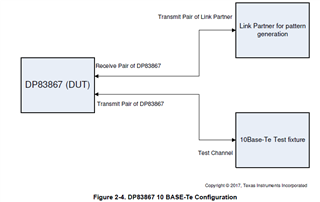

3.10Base-Te Test condition

(1)Test fixture (10Base-Te with TPM):640-0581-001 (EEE-TPA-ERK)

・The above is a test board dedicated to 10Base-Te.

(2)Test PatTern

・at 10BT TEST,Since the link partner cannot output pseudo random,

the pseudo random signal by the PHY BIST (0x16) function was used as the test signal.

◆Below, register settings

0x1f 0x8000, PHY RESET

0x00 0x0100, 10Base-T / Te mode

0x10 0x5008, Forced MDI mode

0x16 0xd804,

(3)oscilloscope:KEYSIGHT

I found a thread related to this issue on the E2E community, but I'm not sure if it was resolved.

Please tell me the following points.

<Question1>

As per the forum answer below, I tried to write the GPHY register.

-------------------------------------------------------------------------------------------

2. For 10BTe :

a. Measure TP_IDL on load 2 (where it was failing earlier) with following extra configuration :

reg<0x009F> = 0xCCCC.

--

Regards,

Vikram

-------------------------------------------------------------------------------------------

By implementing the above settings, the amplitude increased by 0.2V.

Also, the TP_IDL template (LOAD2) now passes.

But it failed with 10BASE-Te peak differential voltage.

・Measured value: 2.129V

・Pass limit: 1.540V <= VALUE <= 1.960

Is it possible to finely adjust the differential amplitude of 10BASE-Te?

Is there any other way to increase the output level?

<Question2>

It was reported that the e2e community and the DP83867 EVM had similar results.

Please let me know the compliance test results of the DP83867 EVM so that I can compare the results.

<Question3>

Has the E2E community issue below been resolved?

e2e.ti.com/.../dp83867ir-10base-te-100base-tx-1000base-t-compliance-test