Hi, I have a problem about the LVDS. I had used the LVDS ICs SN65LVDS307 and SN65LVDS310 to convert VGA data(clock is 6.5MHz). The SN65LVDS307 is the transmitter and SN65LVDS is the reciever. The output LDVS signal of transmitter is fine, clock is 6.5MHz,and |CLK+ - CLK-|=100mV. But reciever is not work.the enable signal, power of the reciever is fine.But the reciever not has output signals, clock and DE of the reciever are LOW,and others signals are HIGH.Please hlep me to work out this probelm.Thank you!

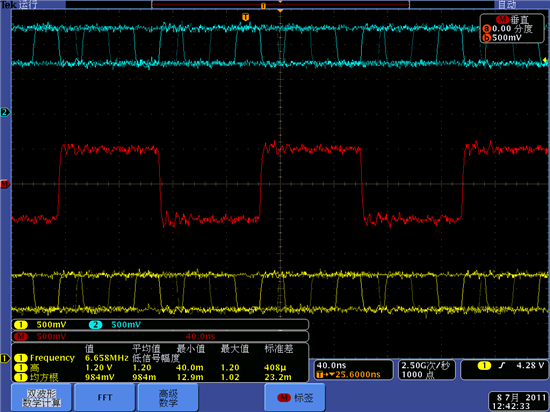

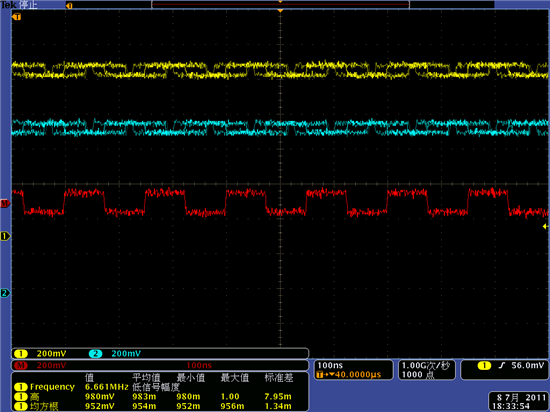

The picture is the output signals of the transmitter. Yellow is CLK+,blue is CLK- and Red is the value of |CLK+ - CLK-|

The picture is the output signals of the transmitter. Yellow is CLK+,blue is CLK- and Red is the value of |CLK+ - CLK-|