Part Number: DP83TC812S-Q1

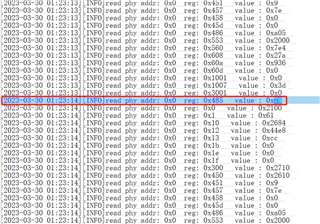

At present, the SAIC side has encountered the problem of blocking the occasional Ethernet message as follows

(1) About the problem description: There are two current problem symptoms

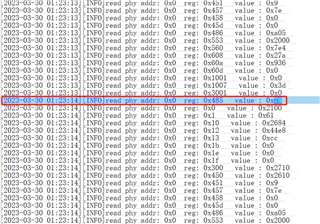

The 1.0x0001 register shows 0x65, i.e., linkup, but Ethernet communication is abnormal.The controller does not receive the opposite message internally and the internal message cannot be forwarded.The scene continues and does not automatically resume.Recover after manual write register 0x1F is 8000.

The 2.0x0001 register shows 0x61, i.e. linkdown, after a few minutes, the state may switch to 0x65.Communication can be automatically resumed during.

(2) Current progress:

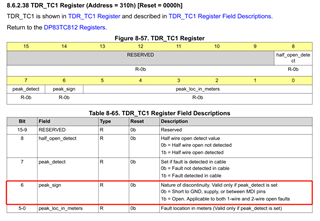

1.Extract all register values before and after the exception to where 0x18h is different by locating them.

0x18 = 481d when the first phenomenon occurs; 0x18 = 5a25 when the second phenomenon occurs;

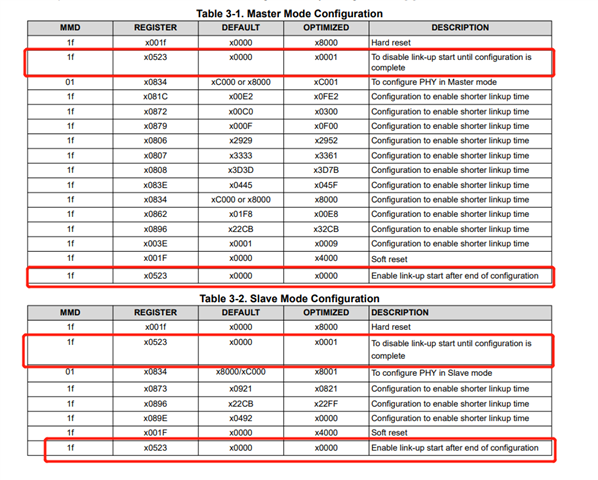

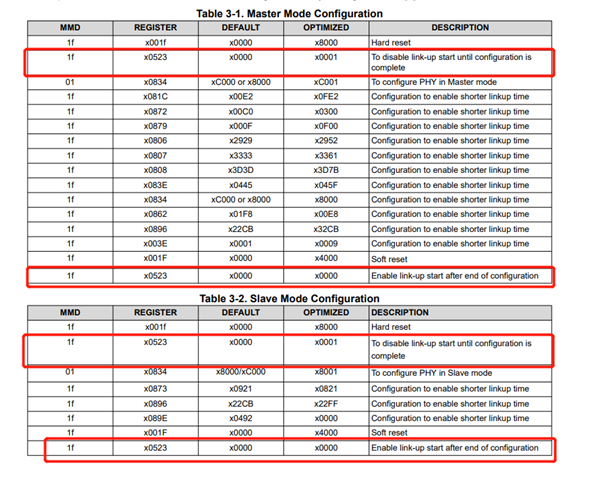

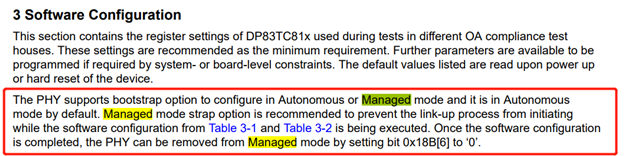

3.By comparing the chip manual, combined with bit9 bit14 reflect, phy may have entered some kind of training mode, especially when the second problem occurs.Enters sleep-related status.

Bit9: 1b = WUP received from remote PHY when in sleep

Bit14: 1b = Link has not been observed within time programmed in 0x562 once training has started

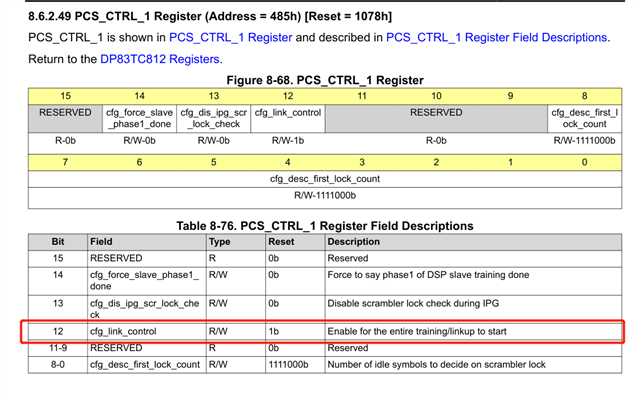

4.The application layer has operated the 0x485 register bit12 to manually control phy linkdown/linkup.However, there is a question about the register bit12:

Bit12: Enable for the entire training/linkage to start

Is Training one of the special modes of the phy chip?Or how do I use this register correctly?XOR How do I properly control phy linkdown/linkup via the registers?