- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi

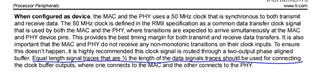

We are using DP83620SQE this in our design. We want to know : whats the length matching tolerance we need to follow for RMII, whether its 2 inches or 50 mils. We are seeing this tolerance different in these reference documents from TI.

Also we want to know if there are any additional guidelines that length of clock needs to be half that of data. This we are finding in AM625x schematics checklist. We are using AM625 processor in our design.

Hi Premalatha,

Here are some comments for following questions:

--

Thank you,

Hillman Lin

Hi

In PHY slave mode ,please confirm if length of the RMII clock trace needs to be equal to that of the data trace or half that of the data trace.

Premalatha,

We are internally assigning this query to processor team to get their feedback about this routing. Team will get back to you shortly.

--

Regards,

Vikram