Other Parts Discussed in Thread: TLK1501, , TLK10081

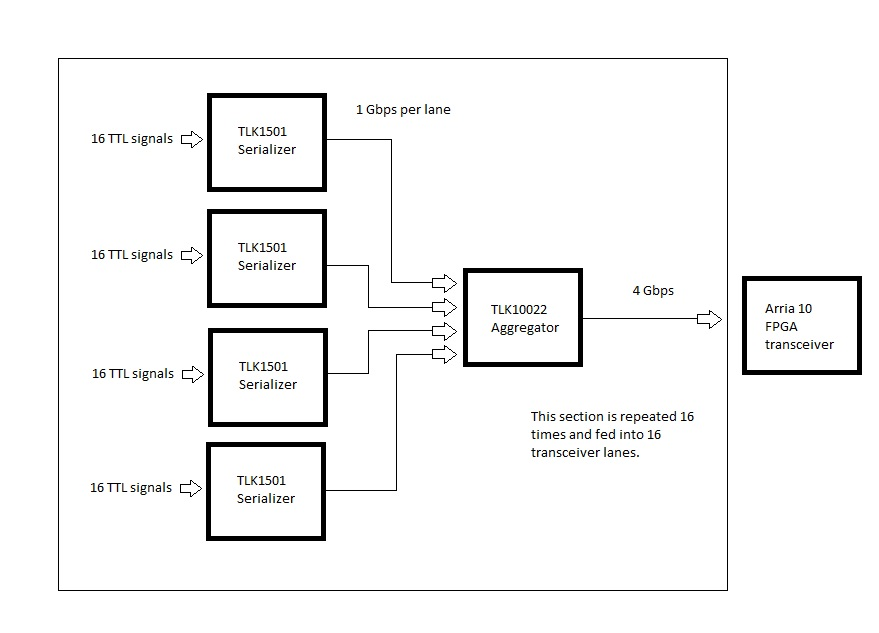

I am planning the setup as shown and the communication will actually be both Tx and Rx between the TLK1501/TLK10022/FPGA. This setup will be repeated 16 times with the same FPGA. I am wondering if the FPGA transceiver will handle the 8B/10B communication automatically or I will have to write some custom interface to handle all the communication. Would it be significantly easier to simply remove the TLK10022 and feed the TLK1501 serial stream into 64 different LVDS channels on the FPGA instead of using the 16 transceiver lanes?